Im Mai 2019 sah es für Huawei schon schlimm genug aus, als die USA das Unternehmen als nationales Unternehmen auf die Unternehmensliste setzten Sicherheitsbedrohung. Infolgedessen konnte Huawei nicht mehr auf seine US-Lieferkette zugreifen. Aber genau ein Jahr später hinderte eine Änderung der US-Exportbestimmungen jede Gießerei, die US-Technologie zur Herstellung von Chips verwendete, daran, hochmoderne Komponenten an Huawei zu liefern.

Selbst die Chips, die Huawei selbst über seine HiSilicon-Einheit entwickelt hatte, durften dies nicht an den Hersteller geliefert werden, was Huawei dazu zwang, seine Kirin 9000 5G-Chips zu rationieren. Und für einige Modelle musste es sich an Qualcomms Snapdragon 888 wenden, jedoch ohne Unterstützung für 5G. Und da die Chipindustrie im nächsten Jahr auf den 3-nm-Prozessknoten umsteigt, wie können die Telefone von Huawei wettbewerbsfähig bleiben, wenn es weiterhin verboten ist, hochmoderne Chips zu erhalten?

Huawei plant, sich mit Chip-Stacking zu befassen, um wettbewerbsfähig zu bleiben

Laut einem Beitrag von Weibo (über Gizchina) ist der derzeit rotierende Vorsitzende von Huawei, Guo Ping sagte kürzlich auf der Konferenz zum Jahresbericht 2021, dass das Unternehmen Chip-Stacking-Technologien einsetzen wird, die es ihm ermöglichen, SoCs zu verwenden, die mit weniger fortgeschrittenen Prozessen gebaut wurden, und dennoch die Leistung von Chips erreichen, die mit fortschrittlicheren Prozessknoten hergestellt wurden. Es gibt einige Vorbehalte, mit denen sich Huawei auseinandersetzen muss, wenn es diesen Plan durchführt.

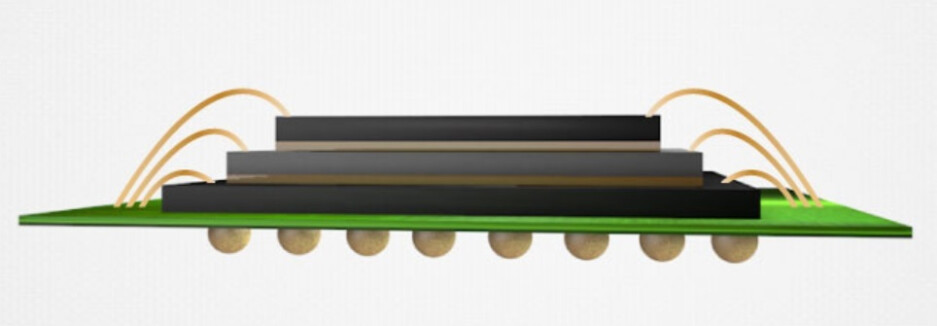

Grundlegendes Bild des Chip-Stapelns mit Chips unterschiedlicher Größe. Credit MasterBond

Das Stapeln von Chips nimmt mehr”Platz”im Inneren eines Telefons ein und könnte auch zusätzliche Wärme erzeugen. Darüber hinaus könnte diese Technologie weniger Platz lassen, um eine Batterie mit großer Kapazität unterzubringen. Wie Sie sich vorstellen können, ist das Stapeln von Chips der Prozess der vertikalen Montage von Chips, um die Leistung zu steigern und den verfügbaren Platz besser zu nutzen.

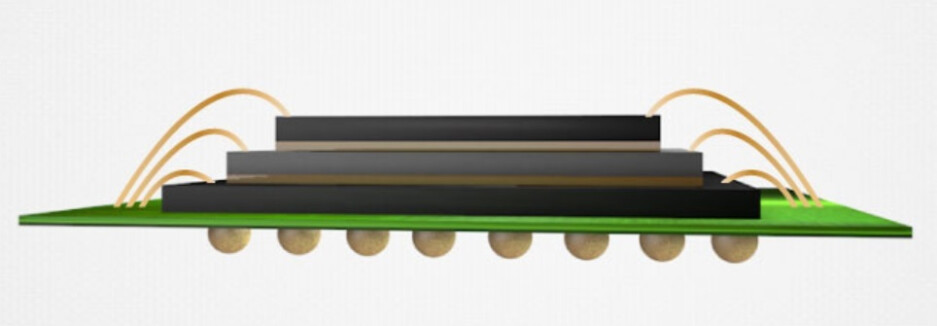

Chip-Stacking mit Chips gleicher Größe

Während er Fragen beantwortete, deutete der Huawei-Manager an, dass das Unternehmen autark sein kann In Bezug auf Chips stellt er fest: „Im Jahr 2019 beliefen sich die Mobiltelefonlieferungen von Huawei auf 120 Millionen Einheiten, was bedeutet, dass 120 Millionen Mobiltelefone Chips benötigen. Im Jahr 2019 beliefen sich die 5G-Basisstationslieferungen von Huawei auf 1 Million Einheiten Chip, es braucht 1 Million. Die beiden Größenordnungen sind völlig unterschiedlich. Huawei kann in zukünftigen Produkten wettbewerbsfähig sein. Wir werden weiter in diese Richtung arbeiten.”

Anfang dieses Monats, Nikkei Asia berichtete, dass drei namhafte Unternehmen, die Gießereien betreiben, TSMC, Samsung und Intel kündigte die Gründung eines Konsortiums an, das sich auf fortschrittliches Chip-Packaging und Chip-Stacking konzentrieren wird. Derzeit ist das Hinzufügen von mehr Transistoren zu einem Chip der Weg, leistungsfähigere Komponenten herzustellen. Aber irgendwann wird die Verkleinerung von Transistoren einen Punkt erreichen, an dem dies nicht mehr möglich ist, und das wird das Ende von Moores Gesetz bedeuten.

Fortschritte in der Chipverpackung könnten das Mooresche Gesetz am Leben erhalten

Sie haben vielleicht schon von Moores Gesetz gehört. Es ist eine Beobachtung von Gordon Moore, dem Mitbegründer von Intel und Fairchild Semiconductor. 1965 erkannte Moore, dass sich die Anzahl der Transistoren auf einer dichten integrierten Schaltung jedes Jahr verdoppelte. Bis 1975 überarbeitete Moore das Mooresche Gesetz und forderte, dass sich die Transistorzahl alle zwei Jahre verdoppeln sollte. Und jetzt, wo wir die Grenzen der Transistorgröße erreichen, nutzt die Industrie mehr Intelligenz als die Teilnehmer einer Wordle-Konferenz, um zu verhindern, dass das Gesetz „aufgehoben“ wird.

Verpackungen sind ein Bereich, in dem wir mehr sehen könnten Innovation in naher Zukunft. Das Konsortium hofft, den Universal Chiplet Interconnect Express (UCIe) zu etablieren, um ein neues Ökosystem zu schaffen und andere Kooperationen in den Segmenten Verpackung und Stacking aufzubauen. Auf der Suche nach einer besseren Mausefalle in Bezug auf das Chip-Packaging haben Unternehmen wie TSMC, Samsung und IBM vertikale Transport-Feldeffekttransistoren (VTFET) entwickelt, die vertikal auf einem Chip gestapelt sind.

Bei VTFET sind die Transistoren senkrecht zueinander angeordnet und der Strom fließt vertikal. IBM und Samsung sagen, dass dieses Design aufgrund des größeren Stromflusses auch zu weniger Energieverschwendung führen wird. Laut den beiden Technologieunternehmen werden Chips, die die VTFET-Transistoren verwenden, in der Lage sein, doppelt so schnell zu arbeiten wie frühere Komponenten oder 85 % weniger Energie zu verbrauchen als Chips, die mit FinFET-Transistoren betrieben werden. Google und AMD sind ebenfalls Teil des Konsortiums mit Samsung, Intel und TSMC. Obwohl Apple kein Mitglied ist, verlässt sich letzteres auf TSMC, um viele seiner Chipdesigns zu bauen, einschließlich der Chips der A-Serie und M-Serie.