Der CEO von AMD hat bestätigt, dass der Nachfolger des auf der CDNA-Architektur basierenden Instinct GPU HPC-Beschleunigers auf dem Weg ist, später in diesem Jahr auf den Markt zu kommen.

AMD Instinct MI200 mit CDNA 2 MCM-GPU-Architektur, die später in diesem Jahr landet, wird HPC-Workloads mit Strom versorgen

Die Bestätigung erfolgte während der 49. jährlichen globalen Technologiekommunikations-und Medienkonferenz von JPMorgan. Lisa Su, CEO von AMD, gab bekannt, dass sie noch in diesem Jahr die nächste Generation der CDNA-Architektur auf den Markt bringen werden. Es folgt das Protokoll der Konferenz (Quelle: Ich suche Alpha ).

Letztes Jahr haben wir über unsere CDNA-Architektur der ersten Generation gesprochen. In diesem Jahr stellen wir, wie gesagt, unsere CDNA-Architektur der nächsten Generation zusammen. Dies ist tatsächlich eine Schlüsselkomponente, die es uns ermöglicht hat, die größten Supercomputer-Angebote in den USA rund um die Ausgabe der Frontier Oak Ridge National Labs sowie die Ausgabe der Lawrence Livermore National Labs mit El Capitan und vielen anderen zu gewinnen.

Es ist jedoch eine kohärente Verbindung zwischen CPUs und GPUs, die es uns ermöglicht, die Optimierung für HPC-und AI-und ML-Anwendungen vollständig durchzuführen. Und wir werden die nächste Generation dieser Architektur später in diesem Jahr auf den Markt bringen. Wir freuen uns sehr darüber. Ich denke, es ist sehr gut vorangekommen. Dies ist der nächste große Schritt in Richtung Innovation in Bezug auf die Rechenzentrumsarchitekturen.

Dr. Lisa Su (CEO von AMD)

Hier ist alles, was wir über AMDs CDNA 2-Architektur-Instinktbeschleuniger wissen

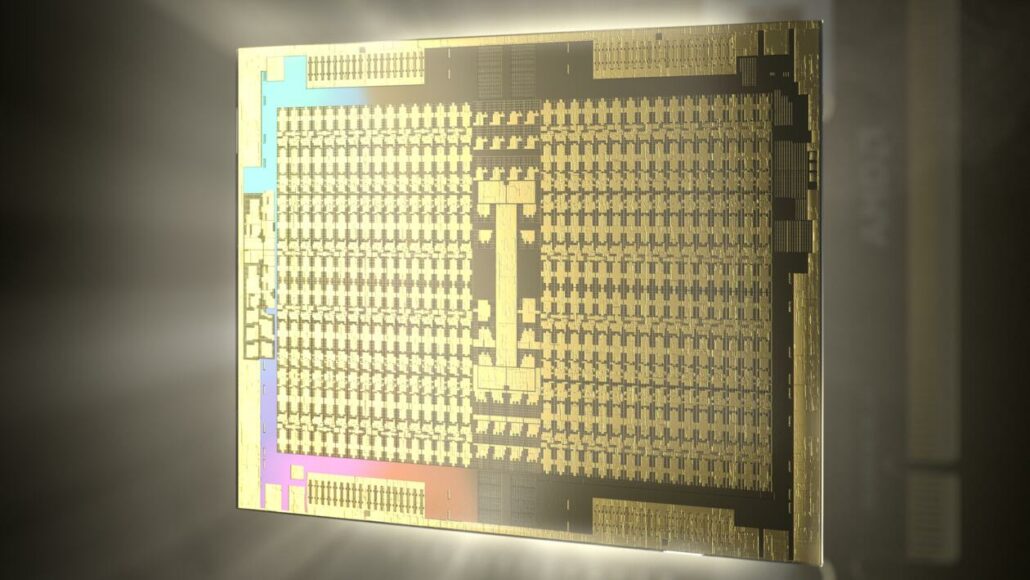

Die AMD CDNA 2-Architektur wird die AMD Instinct HPC-Beschleuniger der nächsten Generation mit Strom versorgen. Wir wissen, dass einer dieser Beschleuniger der MI200 sein wird, der das Ziel Aldebaran GPU . Es wird ein sehr leistungsfähiger Chip und möglicherweise die erste GPU mit MCM-Design. Der Instinct MI200 wird gegen Intels 7-nm-Ponte Vecchio und NVIDIAs aktualisierte Ampere-Teile antreten. Intel und NVIDIA folgen ebenfalls der MCM-Route für ihre HPC-Beschleuniger der nächsten Generation, aber es sieht so aus, als ob Ponte Vecchio wird 2022 verfügbar sein, und das Gleiche gilt für NVIDIAs HPC-Beschleuniger der nächsten Generation als deren eigene Roadmap bestätigt.

Im vorherigen Linux-Patch wurde festgestellt, dass die AMD Instinct MI200-GPU’Aldebaran’HBM2E-Speicherunterstützung bietet. NVIDIA war das erste Unternehmen, das den HBM2E-Standard eingeführt hat, und wird einen schönen Schub gegenüber der Standard-HBM2-Konfiguration bieten, die für den Arcturus-basierten MI100-GPU-Beschleuniger verwendet wird. HBM2E ermöglicht eine Speicherkapazität von bis zu 16 GB pro Stapel, sodass wir für Aldebaran bis zu 64 GB HBM2E-Speicher mit unglaublich hohen Geschwindigkeiten erwarten können.

Der neueste Linux-Kernel-Patch hat ergeben, dass die GPU 16 KB L1-Cache pro CU enthält, was 2 MB des gesamten L1-Cache ausmacht, wenn man bedenkt, dass die GPU 128 Recheneinheiten packen wird. Die GPU enthält auch 8 MB gemeinsam genutzten L2-Cache, jedoch 14 CUs pro Shader Engine im Vergleich zu 16 CUs pro SE in der vorherigen Instinct-Aufstellung. Unabhängig davon wird angegeben, dass jede CU auf Aldebaran-GPUs eine deutlich höhere Rechenleistung aufweist.

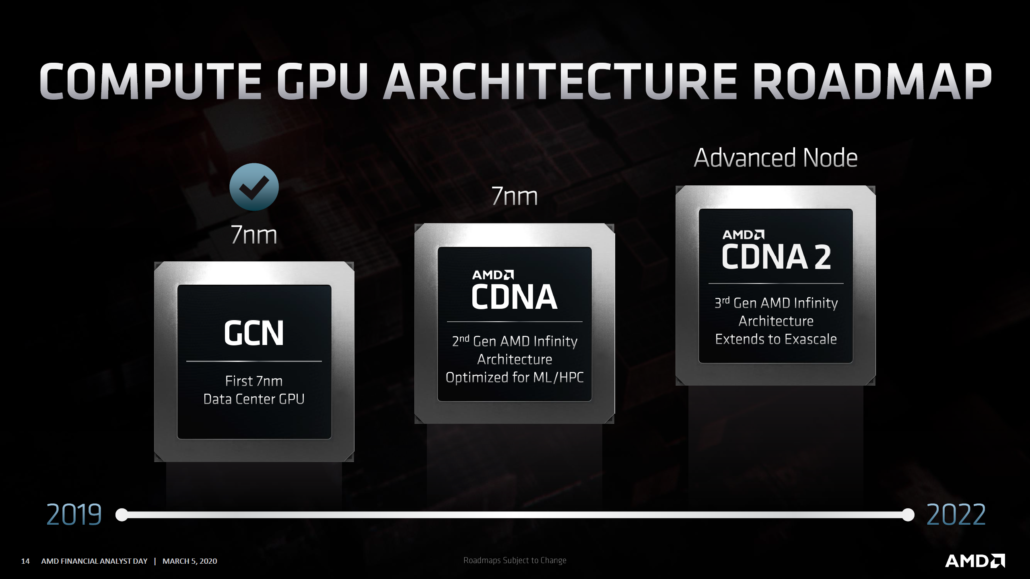

Zu den weiteren aufgeführten Funktionen gehört die SDMA-Unterstützung (System Direct Memory Access), mit der Daten über PCIe-und XGMI/Infinity Cache-Subsysteme übertragen werden können. Soweit Infinity Cache ist besorgt, es sieht so aus, als würde dies auf HPC-GPUs nicht passieren. Beachten Sie, dass die CDNA 2-GPU von AMD auf einem brandneuen Prozessknoten hergestellt wird und eine AMD Infinity-Architektur der 3. Generation aufweist, die sich auf Exascale erstreckt, indem eine kohärente GPU-Konnektivität von bis zu 8-Wege ermöglicht wird

AMD Radeon Instinct Accelerators 2020

| Beschleunigername | AMD Radeon Instinct MI6 | AMD Radeon Instinct MI8 | AMD Radeon Instinct MI25 | AMD Radeon Instinct MI50 | AMD Radeon Instinct MI60 | AMD Instinct MI100 | AMD Instinct MI100 |

|---|---|---|---|---|---|---|---|

| GPU-Architektur | Polaris 10 | Fidschi XT | Vega 10 | Vega 20 | Vega 20 | Arcturus | TBA |

| GPU-Prozessknoten | 14-nm-FinFET | 28 nm | 14 nm FinFET | 7 nm FinFET | 7-nm-FinFET | 7-nm-FinFET | Erweiterter Prozessknoten |

| GPU-Kerne | 2304 | 4096 | 4096 | 3840 | 4096 | 7680 | 7680 x 2 (MCM)? |

| GPU-Taktrate | 1237 MHz | 1000 MHz | 1500 MHz | 1725 MHz | 1800 MHz | ~ 1500 MHz | TBA |

| FP16-Berechnung | 5.7 TFLOPs | 8,2 TFLOPs | 24,6 TFLOPs | 26,5 TFLOPs | 29,5 TFLOPs | 185 TFLOPs | TBA |

| FP32-Berechnung | 5.7 TFLOPs | 8,2 TFLOPs | 12,3 TFLOPs | 13,3 TFLOPs | 14,7 TFLOPs | 23,1 TFLOPs | TBA |

| FP64-Berechnung | 384 GFLOPs | 512 GFLOPs | 768 GFLOPs | 6.6 TFLOPs | 7.4 TFLOPs | 11.5 TFLOPs | TBA |

| VRAM | 16 GB GDDR5 | 4 GB HBM1 | 16 GB HBM2 | 16 GB HBM2 | 32 GB HBM2 | 32 GB HBM2 | TBA |

| Speichertakt | 1750 MHz | 500 MHz | 945 MHz | 1000 MHz | 1000 MHz | 1200 MHz | TBA |

| Speicherbus | 256-Bit-Bus | 4096-Bit-Bus | 2048-Bit-Bus | 4096-Bit-Bus | 4096-Bit-Bus | 4096-Bit-Bus | TBA |

| Speicherbandbreite | 224 GB/s | 512 GB/s | 484 GB/s | 1 TB/s | 1 TB/s | 1,23 TB/s | TBA |

| Formfaktor | Einzelsteckplatz, volle Länge | Doppelsteckplatz, halbe Länge | Doppelsteckplatz, volle Länge | Doppelsteckplatz , Volle Länge | Doppelter Steckplatz, Volle Länge | Doppelter Steckplatz, Volle Länge | OAM |

| Kühlung | Passive Kühlung | Passive Kühlung | Passive Kühlung | Passive Kühlung | Passive Kühlung | Passive Kühlung | Passive Kühlung |

| TDP | 150 W | 300 W | 300 W | 300 W | 300 W | TBA |