El año pasado, la guía de referencia de extensiones ISA actualizada de Intel se actualizó con referencias a Xeon”Sapphire Rapids”que tiene memoria de alto ancho de banda (HBM) con nuevos códigos de error relacionados con HBM. Ahora está aún más claro que están llegando al mercado CPU Xeon con memoria HBM incorporada, ya que Intel ha comenzado a enviar cambios en el controlador del kernel de Linux.

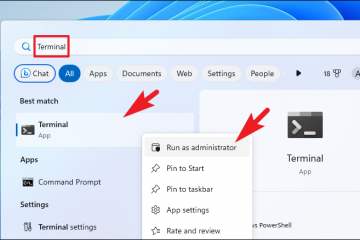

El controlador EDAC i20nm para detección y corrección de errores Los informes se han ampliado para admitir futuras CPU Xeon con memoria HBM incorporada.

Los parches se explican con bastante claridad,” La memoria del paquete viene (en el futuro)… Un futuro procesador Xeon incluirá HBM (memoria de alto ancho de banda) en el paquete. El controlador de memoria HBM en el paquete comparte la misma arquitectura con el controlador de memoria DDR normal. Agregue los dispositivos de controlador de memoria HBM para compatibilidad con EDAC. ”

Hasta ahora, todo indica que la memoria HBM en el paquete se encontrará en SKU selectas de Xeon Sapphire Rapids.

Junto con la compatibilidad con la memoria HBM en el paquete, esta serie de parches EDAC también incluye la adición de compatibilidad con el procesador de red neuronal Ice Lake para la inferencia de aprendizaje profundo (ICL-NNPI) al controlador igen6_edac, así como compatibilidad con Tiger Lake SoC para el controlador de memoria y ECC en banda a este controlador también.

Dado el tiempo de estos parches Intel EDAC, es probable que se fusionen para el kernel de Linux 5.14 en unas pocas semanas.