AMD “big.LITTLE” aha elaborazione eterogenea nella serie Ryzen 8000

Il prossimo decennio non sarà più dettato dal numero di core, ma piuttosto il nodo di fabbricazione del processore, il metodo di confezionamento e l’efficienza energetica. Un ruolo importante sarà svolto anche dalle architetture eterogenee.

Nel corso dell’anno Intel lancerà i suoi processori Core Alder Lake di dodicesima generazione per sistemi desktop e mobili. Questa non è la prima architettura a implementare la tecnologia ibrida di Intel (la prima è stata Lakefield). Questo è un termine di marketing per implementazione core ad alta efficienza (piccola) e ad alte prestazioni (grande). La maggior parte degli utenti di tecnologia dovrebbe avere più familiarità con il termine big.LITTLE, che in realtà è un vecchio nome per l’architettura di elaborazione eterogenea di ARM, ora sostituito da DynamIQ.

Mentre le CPU eterogenee sono state utilizzate nei dispositivi mobili per anni, questa tecnologia non è esattamente un dominio dei moderni PC desktop, in cui l’efficienza energetica non è esattamente la principale preoccupazione. Si dice che il sistema operativo Windows di prossima generazione sia dotato di un nuovo metodo di pianificazione delle attività per un’elaborazione così eterogenea, che potrebbe allinearsi al lancio di Intel Alder Lake.

Anche se AMD non ha davvero confermato che sta funzionando su tale processore design, le perdite ci hanno portato un nuovo nome in codice”Strix Point“, che è associato all’APU basata su Zen5, presumibilmente con anche core più piccoli noti come Zen4D. Quest’ultimo è un nome in codice del core più piccolo.

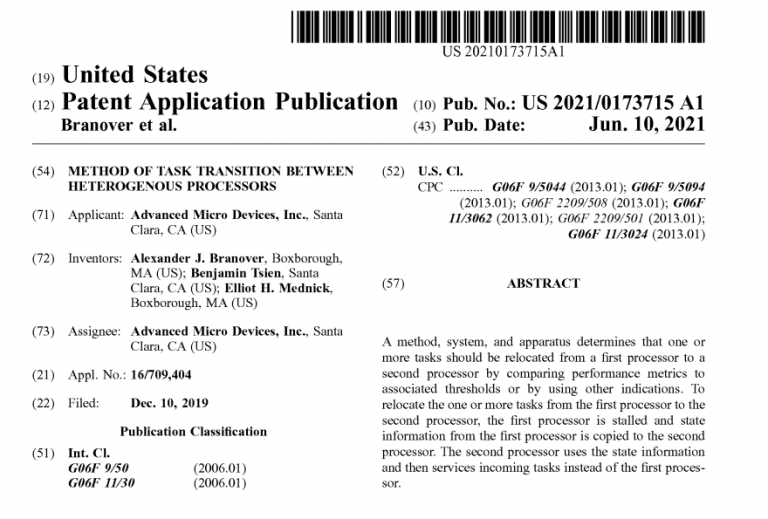

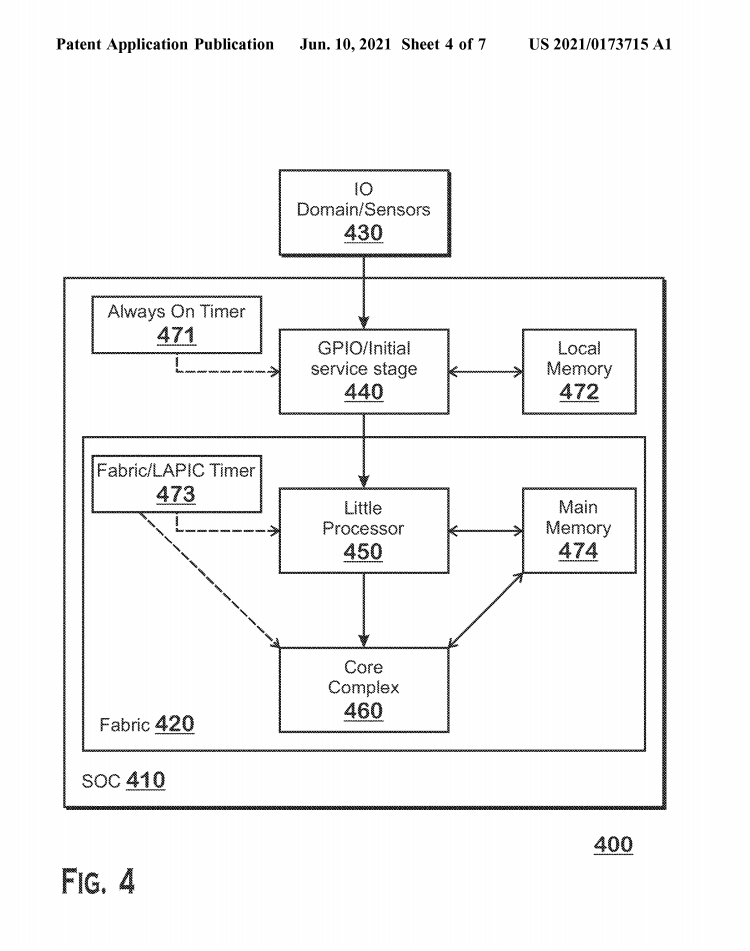

Brevetto AMD”Metodo di transizione delle attività tra processori eterogenei”, Fonte: US Patent Office

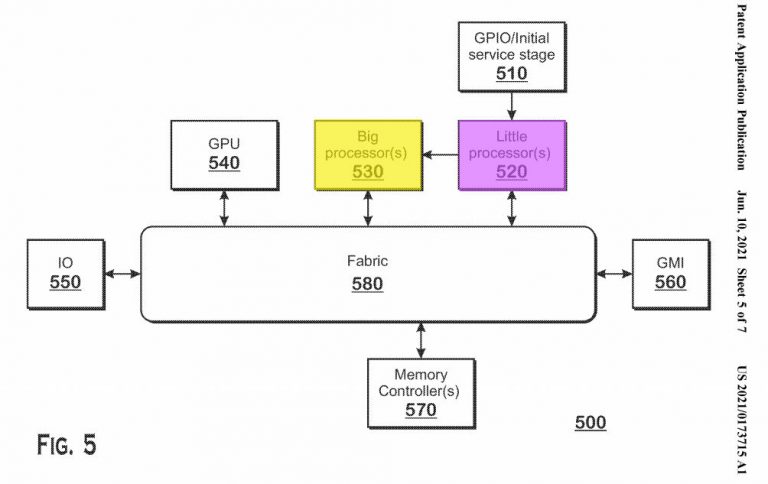

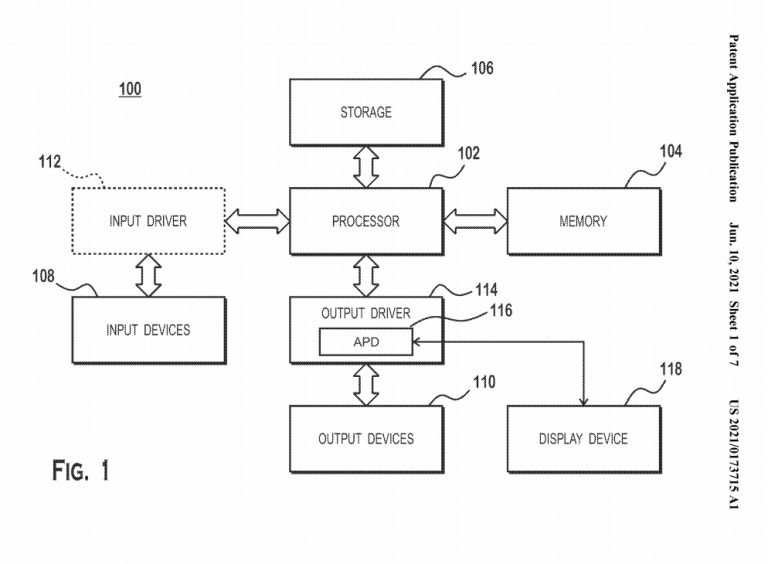

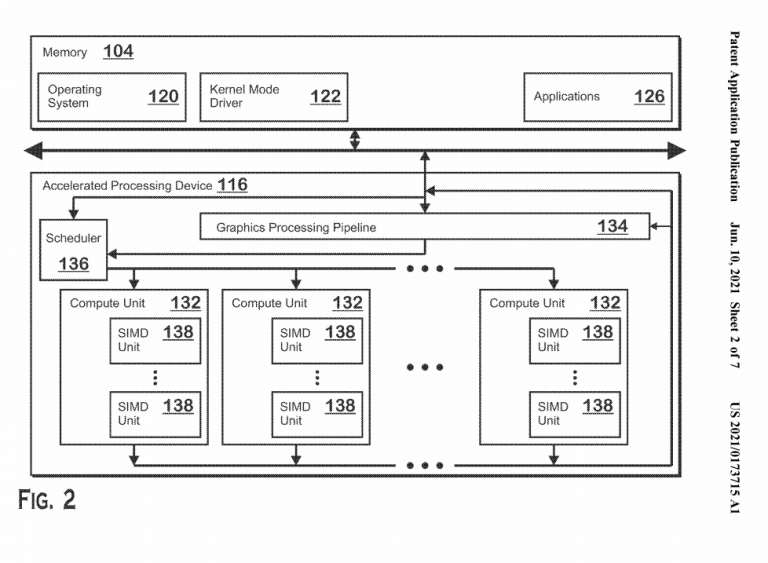

Solo due giorni fa, un brevetto AMD sulla”transizione delle attività tra processori eterogenei” è stato it pubblicato. Questo brevetto è stato originariamente depositato a dicembre 2019, il che suggerisce che AMD ha chiaramente lavorato su questa tecnologia per molto tempo. Il brevetto copre il problema ingegneristico più importante dell’elaborazione eterogenea, ovvero come pianificare o trasferire attività tra diversi tipi di core.

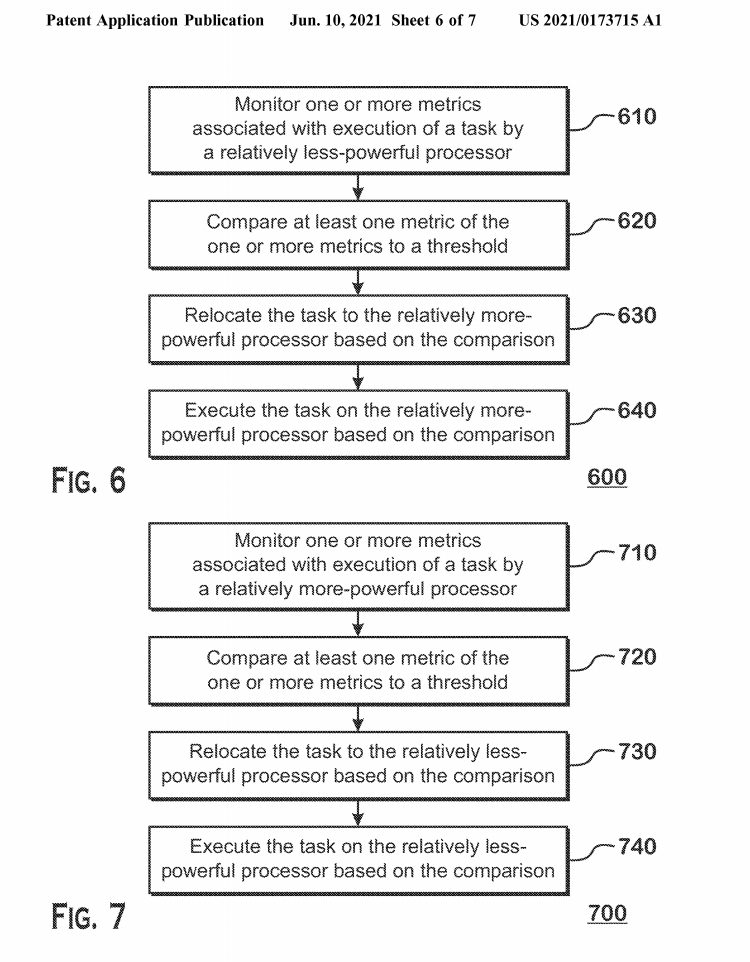

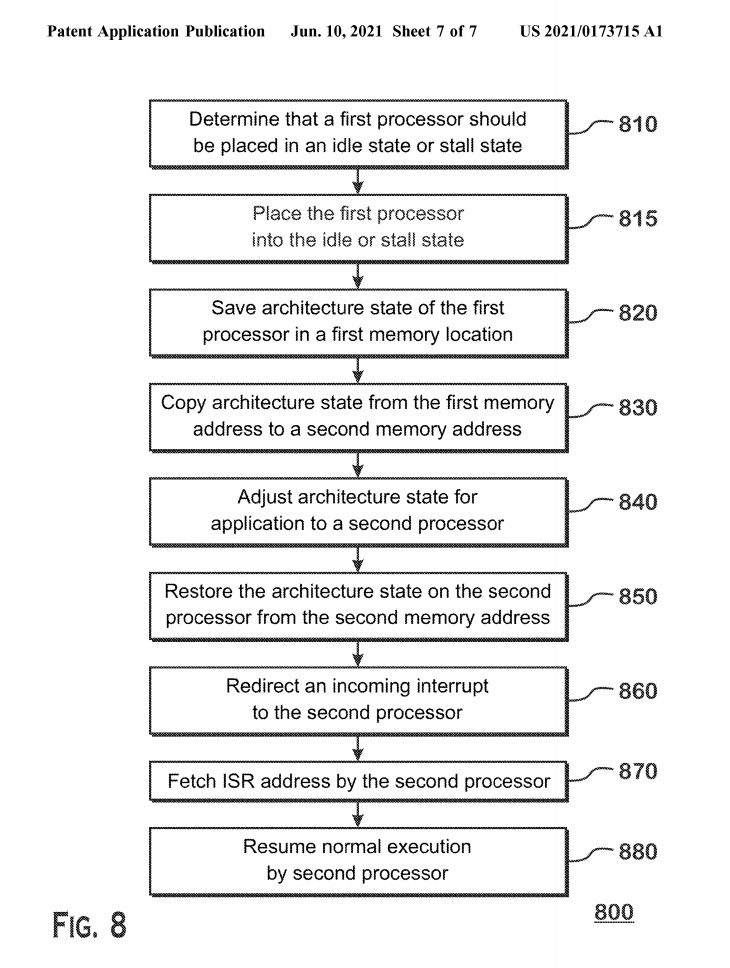

In breve, AMD descrive che la CPU ricollocherà le attività tra i core in base a uno o più metriche. Questi includono il tempo di esecuzione dell’attività, l’obbligo di utilizzare la memoria allo stato di prestazioni massime, l’accesso diretto alla memoria o una metrica della soglia dello stato di inattività medio. Se una qualsiasi di queste metriche (e altre elencate nel brevetto) soddisfa i criteri, l’attività viene quindi trasferita dal primo core del processore al secondo core. Chiaramente, questa non è una descrizione molto dettagliata, ma dovrebbe fornire una breve idea di ciò che viene discusso nel brevetto.

Brevetto AMD “Metodo di transizione tra processori eterogenei”, Fonte: US Patent Office

Brevetto AMD “Metodo di transizione delle attività tra processori eterogenei”, Fonte: US Patent Office

In questo momento, si ritiene che la serie Ryzen 8000 “ Strix Point” sarà la prima di AMD a implementare un’architettura eterogenea con core Zen5 a 3 nm combinati con Zen4D su un singolo pacchetto. Al momento non si dice che una variante desktop con nome in codice”Granite Ridge”sia dotata di un’architettura core grande/piccola. Vale la pena notare che quando saranno disponibili le CPU/APU eterogenee di AMD, Intel avrà già la sua architettura Alder Lake sul mercato. In effetti, è possibile che le prime CPU ibride di AMD debbano competere con il successore di Alder Lake, nome in codice Raptor Lake.

| ROMORED AMD Zen Roadmap | |||||

|---|---|---|---|---|---|

| VideoCardz.com | |||||

| – | |||||

| – | da confermare | da confermare | |||

Fonte: Freepatents tramite @ Kepler_L2