AMD”big.LITTLE”oftewel heterogene computing in de Ryzen 8000-serie

Het volgende decennium zal niet langer worden bepaald door het aantal kernen, maar eerder het fabricageknooppunt, de verpakkingsmethode en de energie-efficiëntie van de processor. Ook heterogene architecturen zullen een grote rol spelen.

Later dit jaar lanceert Intel zijn 12e generatie Core Alder Lake-processors voor desktop-en mobiele systemen. Dit is niet de eerste architectuur die Intel’s hybride technologie implementeert (de eerste was Lakefield). Dit is een marketingterm voor high-efficiency (small) en high-performance (big) core-implementatie. De meeste technische gebruikers zouden meer bekend moeten zijn met de term big.LITTLE, wat eigenlijk een oude naam is voor ARM’s heterogene computerarchitectuur, nu vervangen door DynamIQ.

Hoewel heterogene CPU’s al jaren in mobiele apparaten worden gebruikt, deze technologie is niet bepaald een domein van moderne desktop-pc’s, waar energie-efficiëntie niet bepaald de grootste zorg is. Het gerucht gaat dat het Windows-besturingssysteem van de volgende generatie een nieuwe methode voor taakplanning bevat voor dergelijke heterogene computers, die mogelijk aansluit bij de lancering van Intel’s Alder Lake.

Hoewel AMD niet echt heeft bevestigd dat het aan een dergelijke processor werkt ontwerp hebben de lekken ons een nieuwe codenaam’Strix Point‘opgeleverd, die wordt geassocieerd met op Zen5 gebaseerde APU, vermoedelijk ook met kleinere kernen die bekend staan als Zen4D. De laatste is een codenaam van de kleinere kern.

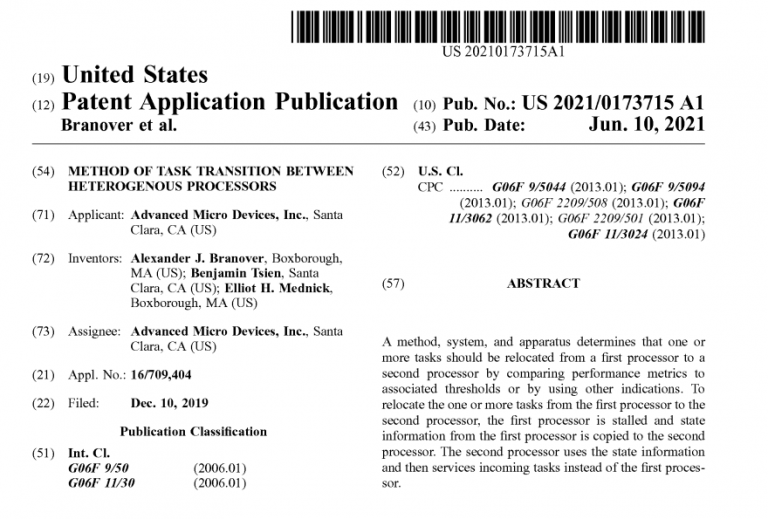

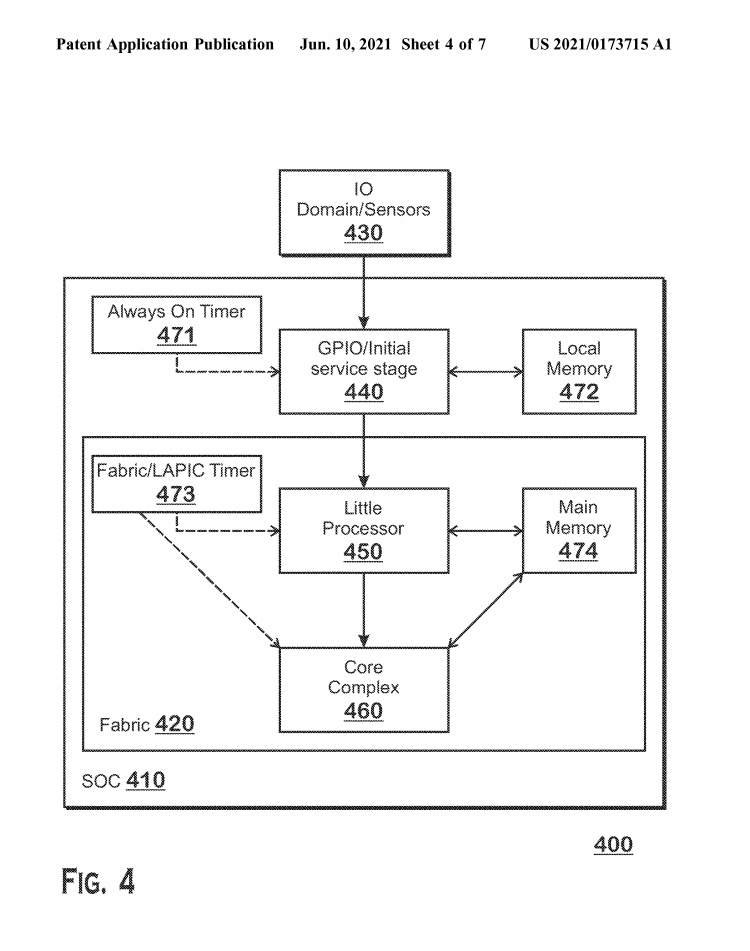

AMD-patent”Method of task transition between heterogene processors”, Bron: US Patent Office

Slechts twee dagen geleden, een AMD-octrooiaanvraag over’task transition between heterogene processors’ is gepubliceerd. Dit patent werd oorspronkelijk ingediend in december 2019, wat suggereert dat AMD duidelijk al lang aan deze technologie werkt. De applicatie behandelt het belangrijkste technische probleem van heterogeen computergebruik, namelijk hoe taken tussen verschillende soorten kernen moeten worden gepland of overgezet.

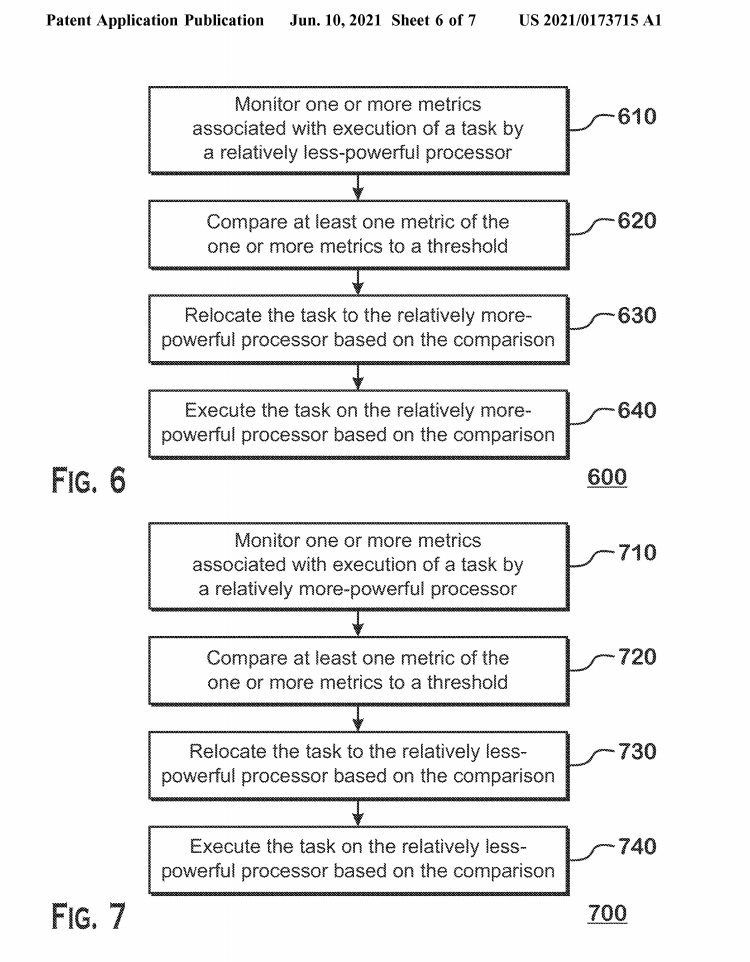

Kortom, AMD beschrijft dat de CPU taken tussen de kernen zal verplaatsen op basis van één of meerdere statistieken. Deze omvatten de uitvoeringstijd van de taak, een vereiste om geheugen te gebruiken bij maximale prestatiestatus, directe toegang tot geheugen of een metriek van de gemiddelde inactieve statusdrempel. Als een van deze (en andere die in het octrooi worden genoemd) voldoen aan de criteria, wordt de taak verplaatst van de eerste processorkern naar de tweede kern. Dit is duidelijk geen erg gedetailleerde beschrijving, maar het zou een kort idee moeten geven van wat er wordt besproken in het patent, dat nog niet is goedgekeurd.

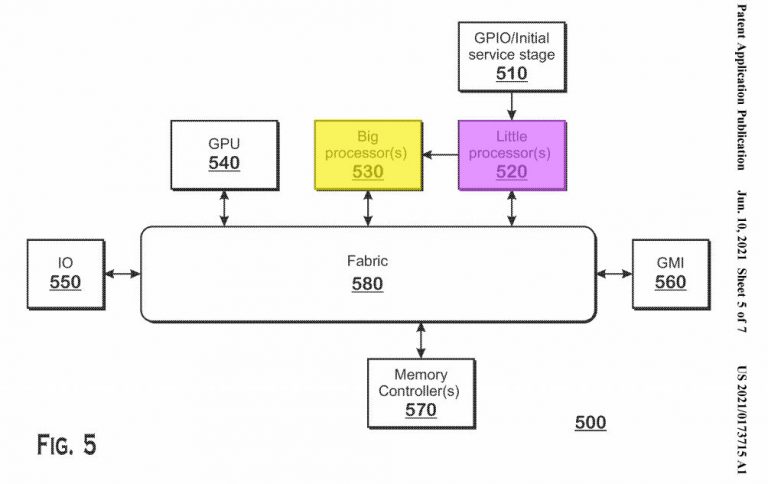

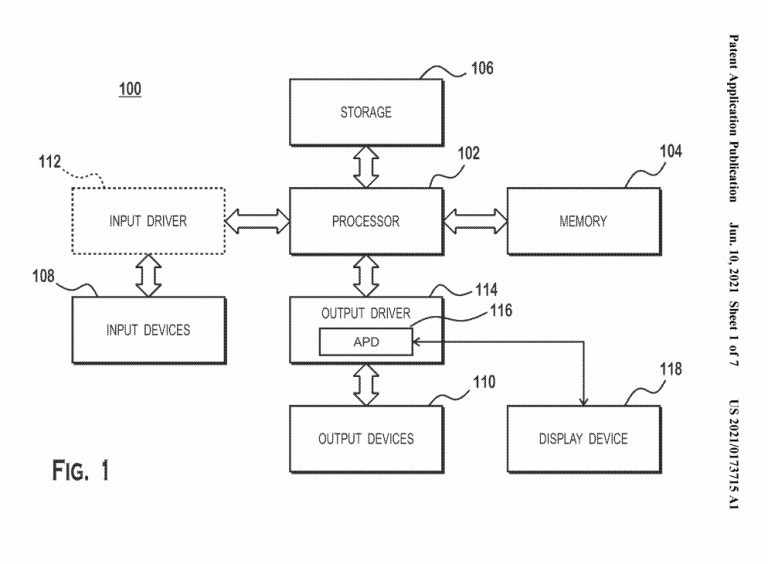

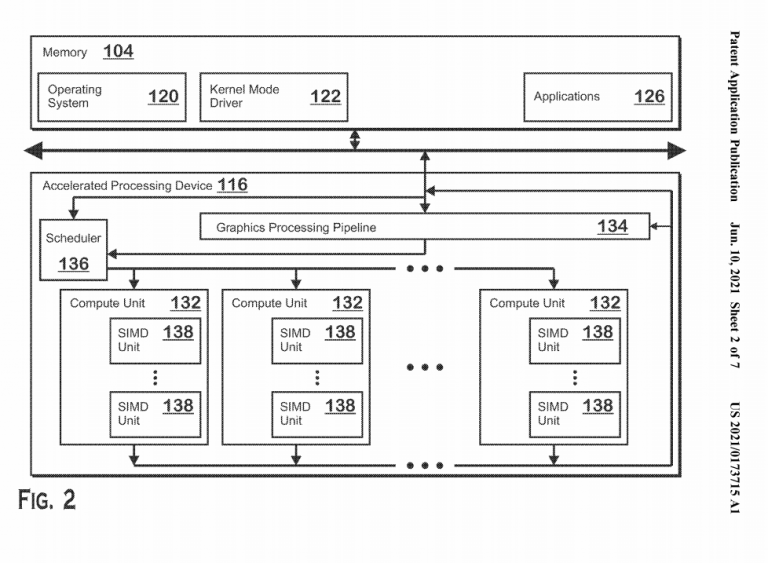

AMD-patent”Werkwijze transitie tussen heterogene processors”, Bron: US Patent Office

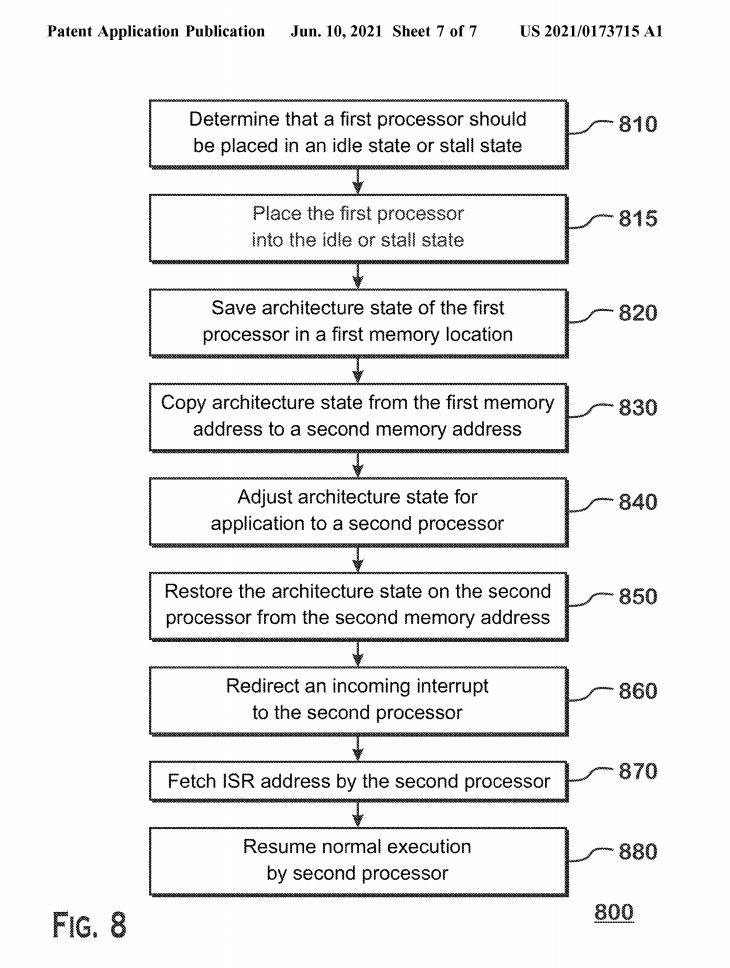

AMD-patent”Method of task transition between heterogene processors”, Bron: US Patent Office

Op dit moment wordt aangenomen dat de Ryzen 8000-serie”Strix Point”AMD’s eerste zal zijn die heterogene architectuur implementeert met 3nm Zen5-kernen gecombineerd met Zen4D op een enkel pakket. Een desktopvariant met de codenaam”Granite Ridge”zou momenteel geen grote/kleine kernarchitectuur hebben. Het is vermeldenswaard dat tegen de tijd dat AMD’s heterogene CPU’s/APU’s beschikbaar zijn, Intel zijn Alder Lake-architectuur al op de markt zal hebben. Het is zelfs mogelijk dat AMD’s eerste hybride CPU’s zullen moeten concurreren met de opvolger van Alder Lake, met de codenaam Raptor Lake.

| GEruchten AMD Zen Roadmap | |||||

|---|---|---|---|---|---|

| VideoCardz.com | |||||

| – | |||||

| – | TBC | TBC | |||

Bron: Vrij patenten via @ Kepler_L2