สิ่งที่ดูไม่ดีพอสำหรับ Huawei ในเดือนพฤษภาคม 2019 เมื่อสหรัฐฯ ติดอันดับรายชื่อนิติบุคคลในระดับชาติ ภัยคุกคามความปลอดภัย ด้วยเหตุนี้ Huawei ไม่สามารถเข้าถึงซัพพลายเชนในสหรัฐฯ ได้อีกต่อไป แต่หนึ่งปีต่อมา การเปลี่ยนแปลงกฎการส่งออกของสหรัฐฯ ทำให้โรงหล่อที่ใช้เทคโนโลยีของสหรัฐฯ ในการสร้างชิปจากการขนส่งส่วนประกอบล้ำสมัยไปยัง Huawei ไม่ได้

แม้แต่ชิปที่ Huawei เองออกแบบผ่านหน่วย HiSilicon ก็ไม่ได้รับอนุญาต ถูกส่งไปยังผู้ผลิตซึ่งบังคับให้ Huawei ปันส่วนชิป Kirin 9000 5G และสำหรับบางรุ่นก็ต้องเปลี่ยนเป็น Snapdragon 888 ของ Qualcomm แต่ไม่รองรับ 5G และด้วยอุตสาหกรรมชิปที่เปลี่ยนไปใช้โหนดกระบวนการ 3nm ในปีหน้า โทรศัพท์ของ Huawei จะสามารถแข่งขันได้อย่างไรหากยังคงถูกห้ามไม่ให้รับชิปที่ล้ำสมัย

Huawei วางแผนที่จะดูที่การซ้อนชิปเพื่อให้สามารถแข่งขันได้

เมื่อเร็ว ๆ นี้ Ping กล่าวในการประชุมรายงานประจำปี 2564 ว่าบริษัทจะใช้เทคโนโลยีการซ้อนชิปเพื่อให้สามารถใช้ SoC ที่สร้างขึ้นโดยใช้กระบวนการที่ก้าวหน้าน้อยกว่า และยังคงตรงกับประสิทธิภาพของชิปที่สร้างโดยใช้โหนดกระบวนการขั้นสูง มีข้อแม้บางประการที่ Huawei จะต้องรับมือหากเป็นไปตามแผนนี้

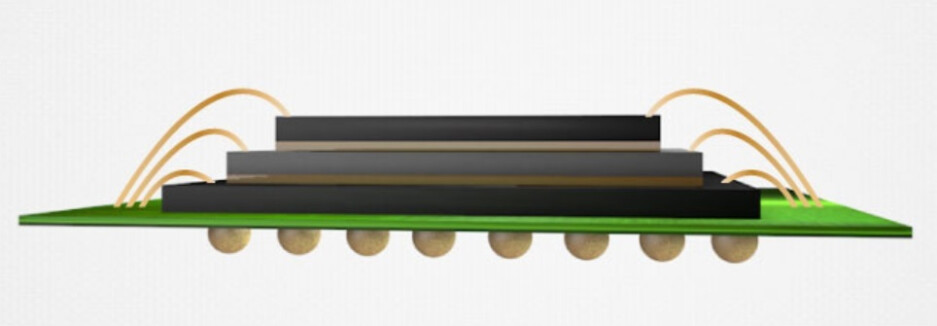

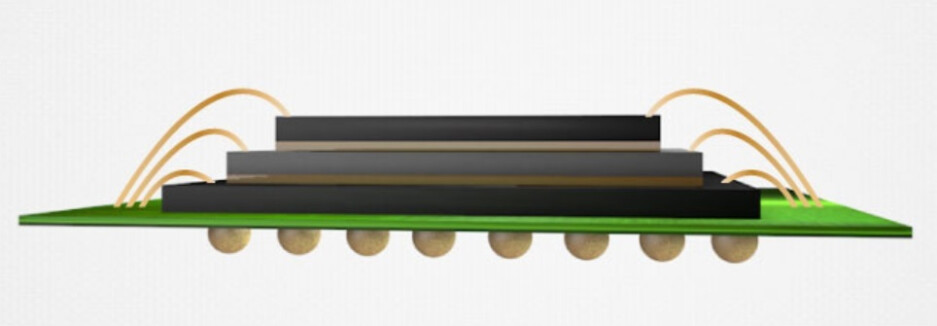

ภาพเบื้องต้นของการซ้อนเศษด้วยแม่พิมพ์ขนาดต่างๆ Credit MasterBond

การซ้อนชิปจะใช้”พื้นที่”มากขึ้นในโทรศัพท์และยังสามารถสร้างความร้อนได้อีกด้วย นอกจากนี้ เทคโนโลยีนี้อาจทำให้มีพื้นที่น้อยลงในการบีบแบตเตอรี่ความจุสูง อย่างที่คุณจินตนาการได้ การวางชิปซ้อนเป็นกระบวนการติดตั้งชิปในแนวตั้งเพื่อเพิ่มประสิทธิภาพและใช้พื้นที่ว่างได้ดียิ่งขึ้น

การซ้อนชิปโดยใช้แม่พิมพ์ขนาดเดียวกัน

ขณะตอบคำถาม ผู้บริหารของ Huawei บอกเป็นนัยว่าบริษัทสามารถพึ่งพาตนเองได้ เมื่อพูดถึงชิป โดยระบุว่า”ในปี 2019 การจัดส่งโทรศัพท์มือถือของ Huawei อยู่ที่ 120 ล้านเครื่อง ซึ่งหมายความว่าโทรศัพท์มือถือ 120 ล้านเครื่องจำเป็นต้องใช้ชิป ในปี 2019 การจัดส่งสถานีฐาน 5G ของ Huawei อยู่ที่ 1 ล้านเครื่อง หากสถานีฐานแต่ละแห่งต้องการชิปเดียว ชิป ต้องใช้ 1 ล้าน ลำดับความสำคัญทั้งสองต่างกันโดยสิ้นเชิง Huawei สามารถแข่งขันกับผลิตภัณฑ์ในอนาคตได้ เราจะทำงานต่อไปในทิศทางนี้”

ต้นเดือนนี้ Nikkei Asia รายงานว่าบริษัทชื่อดังสามแห่งที่ดำเนินธุรกิจโรงหล่อ ได้แก่ TSMC, Samsung และ Intel ประกาศการจัดตั้งกลุ่มที่จะมุ่งเน้นไปที่การบรรจุชิปขั้นสูงและการซ้อนชิป ปัจจุบัน การเพิ่มทรานซิสเตอร์ลงในชิปเป็นวิธีการผลิตส่วนประกอบที่มีประสิทธิภาพมากขึ้น แต่ในที่สุด การย่อขนาดของทรานซิสเตอร์จะถึงจุดที่ไม่สามารถทำได้อีกต่อไปและนั่นจะหมายถึงจุดสิ้นสุดของกฎของมัวร์

ความก้าวหน้าในการบรรจุชิปอาจทำให้กฎของมัวร์ยังมีชีวิตอยู่

คุณอาจเคยได้ยินเกี่ยวกับกฎของมัวร์ เป็นการสังเกตที่ทำโดย Gordon Moore ผู้ร่วมก่อตั้งของ Intel และ Fairchild Semiconductor ในปีพ.ศ. 2508 มัวร์ตระหนักว่าจำนวนทรานซิสเตอร์บนวงจรรวมแบบหนาแน่นนั้นเพิ่มขึ้นเป็นสองเท่าทุกปี ภายในปี 1975 มัวร์ได้แก้ไขกฎของมัวร์ที่เรียกร้องให้จำนวนทรานซิสเตอร์เพิ่มขึ้นเป็นสองเท่าทุก ๆ สองปี และตอนนี้ เมื่อเราบรรลุข้อจำกัดด้านขนาดทรานซิสเตอร์ อุตสาหกรรมกำลังใช้พลังงานสมองมากกว่าผู้เข้าร่วมในการประชุม Wordle เพื่อพยายามป้องกันไม่ให้กฎหมาย”ถูกยกเลิก”

บรรจุภัณฑ์เป็นพื้นที่หนึ่งที่เราจะได้เห็นมากขึ้น นวัตกรรมในระยะใกล้ สมาคมหวังที่จะจัดตั้ง Universal Chiplet Interconnect Express (UCIe) เพื่อสร้างระบบนิเวศใหม่และช่วยสร้างความร่วมมืออื่นๆ ในกลุ่มบรรจุภัณฑ์และการซ้อน มองหากับดักหนูที่ดีกว่าในแง่ของบริษัทชั้นนำด้านบรรจุภัณฑ์ชิป เช่น TSMC, Samsung และ IBM เพื่อพัฒนา Vertical Transport Field Effect Transistors (VTFET) ที่เรียงซ้อนกันในแนวตั้งบนชิป

ด้วย VTFET ทรานซิสเตอร์จะถูกวางในแนวตั้งฉากกัน และกระแสไหลในแนวตั้ง IBM และ Samsung กล่าวว่าการออกแบบนี้จะทำให้สิ้นเปลืองพลังงานน้อยลงเนื่องจากกระแสไฟไหลมากขึ้น ตามที่บริษัทเทคโนโลยีทั้งสองกล่าว ชิปที่ใช้ทรานซิสเตอร์ VTFET จะสามารถทำงานได้เร็วกว่าส่วนประกอบก่อนหน้านี้ถึง 2 เท่า หรือใช้พลังงานน้อยกว่าชิปที่ขับเคลื่อนโดยทรานซิสเตอร์ FinFET ถึง 85%

Google และ AMD ก็เป็นส่วนหนึ่งของกลุ่มความร่วมมือด้วย ซัมซุง อินเทล และ TSMC แม้ว่า Apple จะไม่ใช่สมาชิก แต่ฝ่ายหลังก็พึ่งพา TSMC ในการสร้างการออกแบบชิปหลายแบบรวมถึงชิป A-series และ M-series