AMD EPYC Genoa com suporte de memória DDR5-5200 de 12 canais

Alguns dias depois AMD adicionou patches do Linux confirmando a configuração de memória AMD EPYC Genoa, duas fontes corroboraram a história compartilhando documentos ainda não divulgados.

Os patches confirmaram que o AMD EPYC “Genoa” que é baseado na microarquitetura Zen4 irá de fato suportar memória 1DPC DDR5 de 12 canais. No entanto, isso não é exatamente uma notícia neste momento, mas a primeira vez que a própria AMD confirmou. A razão pela qual isso era conhecido há alguns meses é que alguns documentos que fizeram parte do vazamento da Gigabyte/AMD na verdade incluíram informações extensas sobre a série EPYC de próxima geração. Até agora, esses documentos não foram publicados.

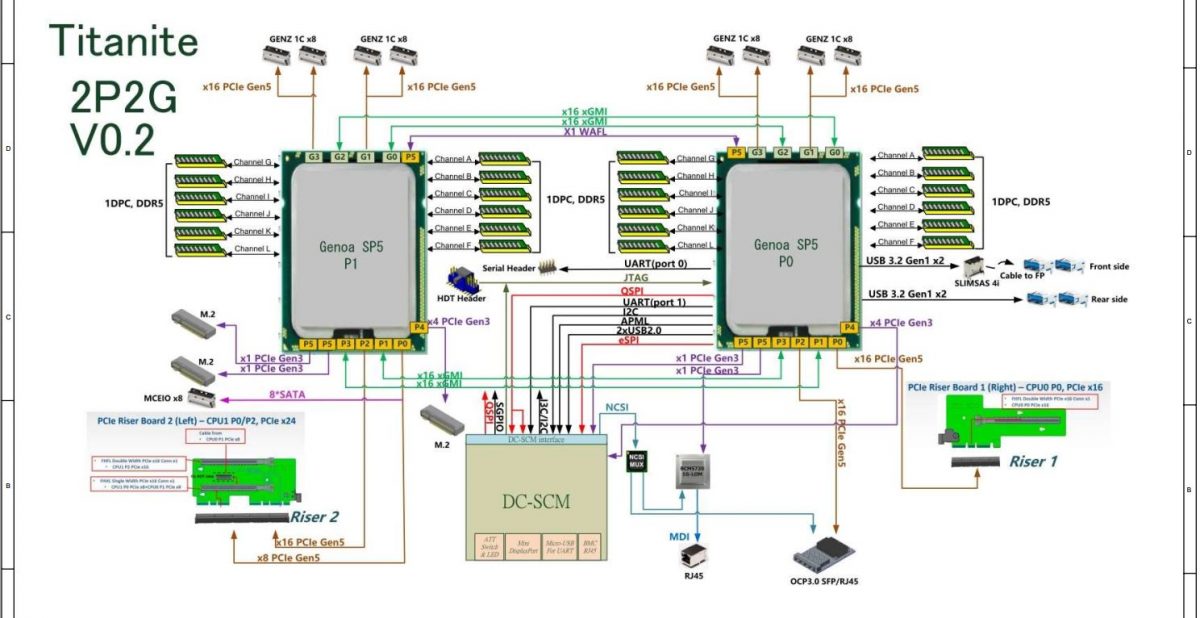

O primeiro documento postado por Hans de Vries mostra um diagrama do sistema Titanite 2P2G com CPU dupla Genoa SP5, cada uma suportando até doze módulos DDR5 ao mesmo tempo. Não sabemos quão preciso e atualizado é este diagrama, no entanto, deve-se notar que de acordo com esta imagem, esperava-se que Gênova suportasse Gen-Z, mas no final, a AMD decidiu oferecer suporte ao padrão CXL (como na foto acima). O Consórcio Gen-Z confirmou que irá transferir as especificações da interface para o consórcio CXL, o que torna Gen-Z praticamente abandonado neste ponto. Independentemente de ser GenZ ou CXL, ele ainda contará com o padrão PCIe Gen5.

Sistema Titanite 2P2G com CPU dupla Genoa SP5, Fonte: Hans de Vries

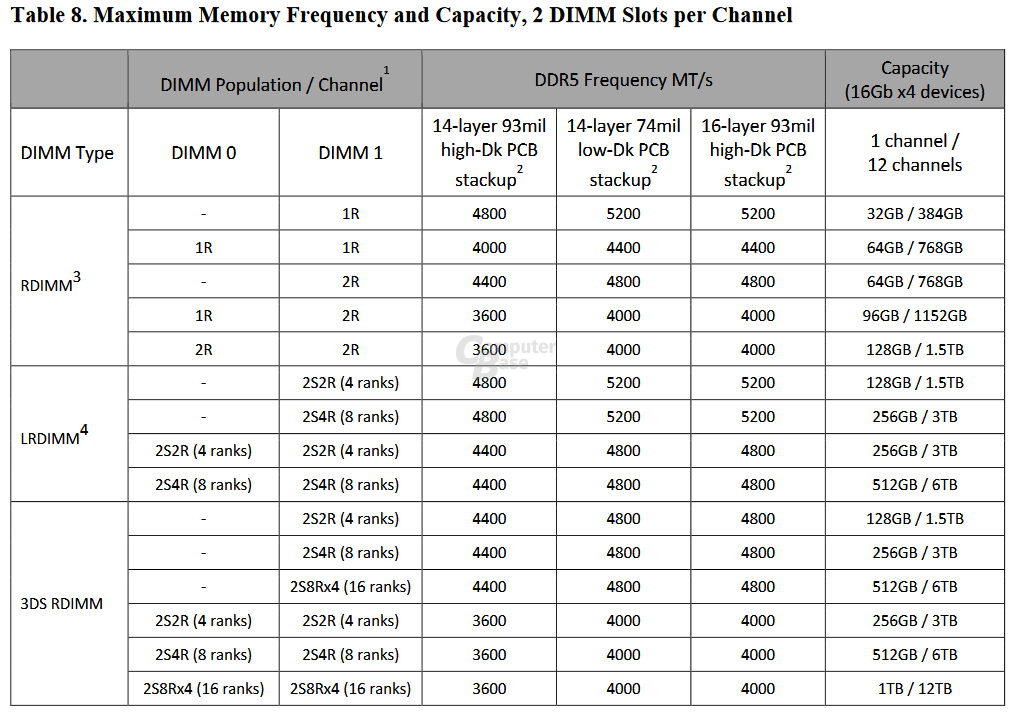

ComputerBase postou uma captura de tela da apresentação de suporte de memória AMD Genoa. Ele confirma que a próxima geração de CPU EPYC deve suportar até 5200 MT/s por meio de módulos de memória de 16 camadas com capacidade de até 1,5 TB (tipo LRDIMM). Curiosamente, a plataforma é capaz de suportar até 12 TB com módulos RDIMM 3DS (o 3DS usa vias de silício); no entanto, a velocidade será limitada a 4000 MT/s.

Suporte de memória AMD EPYC Genoa, Fonte: ComputerBase

A AMD confirmou que Gênova agora está fazendo amostragem para os clientes e está prestes a ser lançado em 2022. Será acompanhado por Bergamo baseada na microarquitetura Zen4c que será compatível com o soquete e a plataforma SP5.

Fonte: ComputerBase , @HansDeVriesNL via TechPowerUP