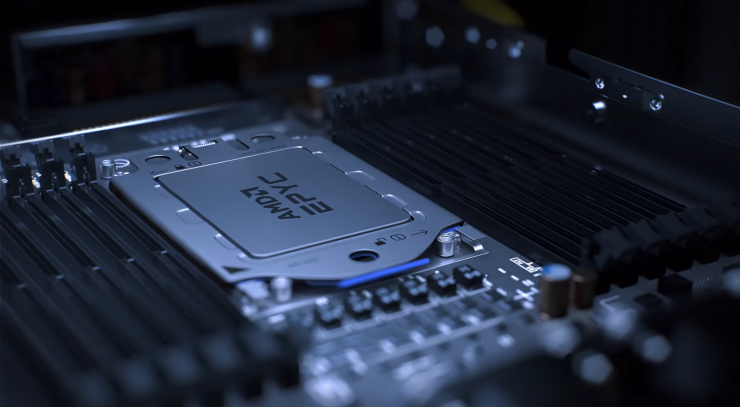

CPUs EPYC Milan-X de próxima geração da AMD que irão A embalagem do 3D Chiplet vazou por Momomo_US . A linha servirá como uma solução intermediária antes que a linha EPYC Genoa com Zen 4 chegue no final de 2022-2023.

Os SKUs de CPU do servidor EPYC Milan-X da AMD vazam, até 64 núcleos com V-Cache 3D Tecnologia?

A AMD confirmou até agora que está trazendo a tecnologia de empilhamento de chips V-Cache 3D para sua arquitetura de núcleo Zen 3. A tecnologia seria introduzida pela primeira vez nas CPUs Ryzen Desktop de próxima geração e, ao que parece, outro produto importante em desenvolvimento com 3D V-Cache é o Milan-X. O AMD Milan-X é conhecido há um tempo e será semelhante às CPUs Milan EPYC 7003 existentes, exceto que receberá grandes mudanças na forma de empilhamento de chips.

EPYC 73 ○○ X

(੭ ु´ ・ ω ・ `) ੭ ु⁾⁾-188 号 (@momomo_us) 25 de agosto de 2021

A seguir estão os SKUs AMD EPYC 7003X Milan-X que vazaram:

EPYC 7773X 64 Core (100-000000504) EPYC 7573X 32 Core (100-000000506) EPYC 7473X 24 Core (100-000000507) EPYC 7373X 16 Core (100-000000508)

Curiosamente, todos os quatro SKUs listados aqui retêm as mesmas contagens de núcleo como variantes atuais, então não veremos CCD sobre o nível de empilhamento de CCD tão cedo. Os CCDs retêm sua contagem de cache integral, mas obterão um impulso do cache SRAM adicionado por meio do empilhamento de chips.

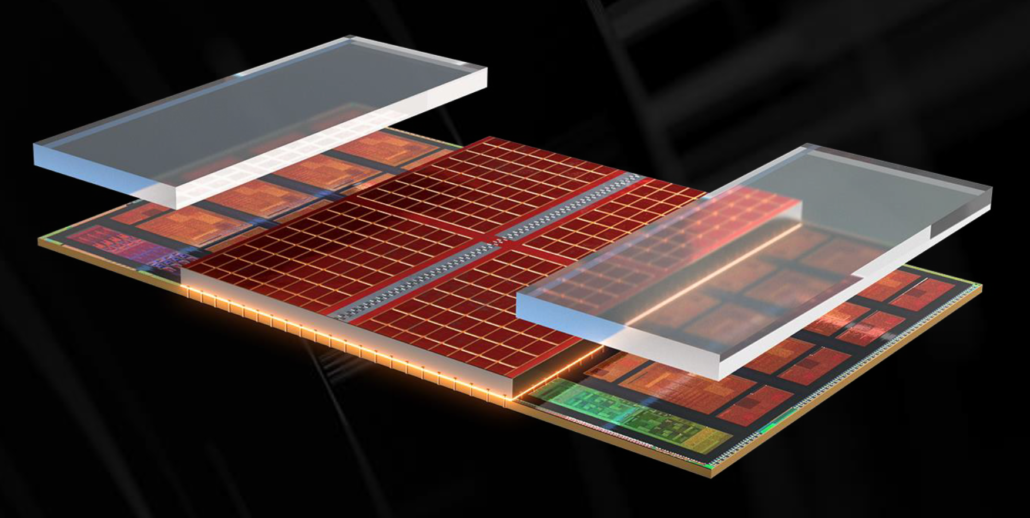

Agora, o que sabemos sobre a tecnologia 3D V-Cache é que ela é alcançada por meio do uso de Micro Bump (3D) e várias interconexões TSV. A interconexão usa uma nova ligação dielétrica-dielétrica hidrofílica com ligação CU-CU direta que foi projetada e co-otimizada em parceria com a TSMC. Os dois silicones individuais (chips) são unidos por meio dessa tecnologia. A tecnologia 3D apresenta ligações de 9 Micron Pitch.

Uma única pilha 3D V-Cache incorporaria 64 MB de cache L3 que fica em cima dos TSVs já apresentados no Zen existente 3 CCDs. O cache será adicionado aos 32 MB existentes de cache L3 para um total de 96 MB por CCD. A AMD também afirmou que a pilha V-Cache pode ir até 8-hi, o que significa que um único CCD pode tecnicamente oferecer até 512 MB de cache L3 além do cache de 32 MB por Zen 3 CCD. Portanto, com 64 MB de cache L3, você pode tecnicamente obter até 768 MB de cache L3 (8 pilhas CCD V-Cache 3D=512 MB), o que será um aumento gigantesco no tamanho do cache.

3D V-Cache poderia ser apenas um aspecto da linha EPYC Milan-X. A AMD pode introduzir clocks mais rápidos à medida que 7nm continua a amadurecer e podemos ver um desempenho muito mais rápido desses chips empilhados. Também é interessante que os códigos OPN para esses processadores estejam prontos, o que significa que um lançamento no final de 2022 é altamente provável, o que significaria que Milan-X pode ser o primeiro chip a introduzir 3D V-Cache.