«comunicado à imprensa»

Synopsys acelera designs de matriz múltipla com as primeiras soluções completas HBM3 IP e de verificação da indústria

Destaques deste anúncio:

O DesignWare HBM3 Controller, PHY e Verification IP reduz o risco de integração e maximiza o desempenho da memória em sistemas multi-die 2.5D Controlador HBM3 de baixa latência com opções de configuração flexíveis que aumentam a largura de banda da memória Pré endurecido ou configurável HBM3 PHY em processo de 5 nm opera a 7200 Mbps para até 2X a taxa de dados e melhora a eficiência de energia em até 60% em comparação com HBM2E Verification IP e modelos de memória para ZeBu e HAPS oferecem um fim a fim solução para fechamento de verificação rápida de IP para o Compilador 3DIC da SoC Synopsys, um projeto integrado de múltiplas matrizes e plataforma de análise rm, fornece uma solução de roteamento automático HBM3 abrangente para desenvolvimento de design rápido e robusto

Synopsys, Inc. (Nasdaq: SNPS) anunciou hoje a primeira solução HBM3 IP completa da indústria, incluindo controlador, PHY e verificação IP para multi 2,5D sistemas de pacotes-die. A tecnologia HBM3 ajuda os designers a atender aos requisitos essenciais de alta largura de banda e memória de baixo consumo de energia para designs de sistema em chip (SoC) visando computação de alto desempenho, IA e aplicativos gráficos. O Controlador DesignWare® HBM3 da Synopsys e o PHY IP, construído com base no HBM2E IP comprovado em silício, alavancam a experiência de interposer da Synopsys para fornecer uma solução de baixo risco que permite alta largura de banda de memória de até 921 GB/s.

A solução de verificação Synopsys, incluindo Verification IP com cobertura embutida e planos de verificação, modelos de memória HBM3 prontos para emulação ZeBu® e sistema de prototipagem HAPS®, acelera a verificação de HBM3 IP para SoCs. Para acelerar o desenvolvimento de projetos de sistema HBM3, a plataforma de projeto de múltiplas matrizes 3DIC Compiler da Synopsys oferece uma exploração arquitetônica totalmente integrada, implementação e solução de análise em nível de sistema.

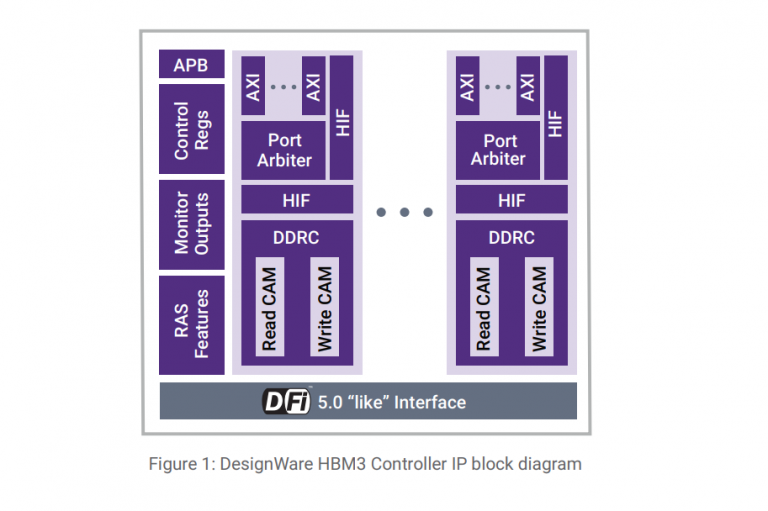

O DesignWare HBM3 Controller IP da Synopsys suporta uma variedade de HBM3 com base em sistemas com opções de configuração flexíveis. O controlador minimiza a latência e otimiza a integridade dos dados com recursos RAS avançados que incluem código de correção de erros, gerenciamento de atualização e paridade.

O DesignWare HBM3 PHY IP em processo de 5 nm, disponível como PHY pré-endurecido ou configurável pelo cliente , opera a até 7200 Mbps por pino, melhora significativamente a eficiência energética e suporta até quatro estados operacionais ativos, permitindo o escalonamento de frequência dinâmico. O DesignWare HBM3 PHY utiliza um micro bump array otimizado para ajudar a minimizar a área. O suporte para comprimentos de rastreamento de interposer dá aos designers mais flexibilidade na colocação de PHY sem afetar o desempenho.

O Synopsys Verification IP para HBM3 usa a arquitetura SystemVerilog Universal Verification Methodology nativa de próxima geração para facilitar a integração de ambientes de verificação existentes e executar um maior número de testes, acelerando o tempo para o primeiro teste. Os modelos de memória HBM3 prontos para uso para emulação ZeBu e sistema de prototipagem HAPS permitem a verificação de RTL e software para níveis mais altos de desempenho.

“A Synopsys continua a atender aos requisitos de design e verificação de SoCs intensivos em dados com IP de interface de memória de alta qualidade e soluções de verificação para os protocolos mais avançados, como HBM3, DDR5 e LPDDR5 ”, disse John Koeter, vice-presidente sênior de marketing e estratégia para IP da Synopsys. “As soluções completas HBM3 IP e verificação permitem que os designers atendam aos crescentes requisitos de largura de banda, latência e energia enquanto aceleram o fechamento da verificação, tudo de um único provedor confiável.”

O amplo portfólio DesignWare IP da Synopsys inclui bibliotecas lógicas, memórias incorporadas, sensores PVT, teste incorporado, IP analógico, IP de interface, IP de segurança, processadores e subsistemas incorporados. Para acelerar a prototipagem, o desenvolvimento de software e a integração de IP em SoCs, a iniciativa IP Accelerated da Synopsys oferece kits de prototipagem de IP, kits de desenvolvimento de software de IP e subsistemas de IP. Nosso amplo investimento em qualidade IP e suporte técnico abrangente permitem que os designers reduzam o risco de integração e acelere o tempo de colocação no mercado.

Apoiando as cotações de clientes e parceiros

“A Micron está empenhada em capacitar os sistemas de computação mais avançados do mundo com as soluções de melhor desempenho do setor. O HBM3 fornecerá a largura de banda de memória crítica para permitir a próxima geração de sistemas de computação de alto desempenho e inteligência artificial ”, disse Mark Montierth, vice-presidente da Micron e gerente geral de memória e rede de alto desempenho. “Nossa colaboração com a Synopsys acelerará o desenvolvimento do ecossistema para produtos HBM3 de largura de banda ultra-alta e eficientes em energia com desempenho sem precedentes.”

“A era orientada por dados de computação e evolução de IA, HPC, gráficos e outros os aplicativos aumentaram exponencialmente os requisitos de largura de banda de memória ”, disse Kwangil Park, vice-presidente sênior de Planejamento de Produto de Memória da Samsung Electronics. “Como líder mundial na fabricação de chips de memória, a Samsung está continuamente focada no suporte à prontidão do ecossistema e no desenvolvimento do HBM para atender aos crescentes requisitos de largura de banda em todos os aplicativos. A Synopsys é pioneira do ecossistema na indústria HBM e um parceiro valioso. Esperamos continuar a fornecer o melhor desempenho de HBM aos nossos clientes. ”

“ SK hynix, um fabricante líder global de semicondutores, continua a investir no desenvolvimento de tecnologias de memória de próxima geração, incluindo HBM3 DRAMs, para atender o crescimento exponencial em cargas de trabalho para aplicativos gráficos e de IA ”, disse Cheol Kyu Park, vice-presidente, campeão de produto da HBM e chefe de engenharia de produto DRAM da SK hynix. “Vamos alavancar nosso relacionamento de longa data com a Synopsys para fornecer aos nossos clientes mútuos soluções HBM3 totalmente testadas e interoperáveis que podem maximizar o desempenho, capacidade e rendimento da memória.”

“Socionext, um líder global em SoC soluções, junto com a Synopsys, um parceiro líder do setor, fornecem soluções abrangentes aos nossos clientes em uma ampla gama de mercados ”, disse Yutaka Hayashi, vice-presidente de Data Center & Networking Business Unit da Socionext. “Nossa recente colaboração com a Synopsys, aproveitando o HBM2E IP da Synopsys em um processo de 5 nm e uma plataforma de design de múltiplas matrizes de sistema completo integrado, se estenderá para incluir o novo DesignWare HBM3 IP e soluções de verificação. Como resultado, nossos clientes podem obter maior desempenho e capacidade de memória em SoCs que exigem a especificação HBM3 que está por vir. ”

Disponibilidade e recursos

O controlador Synopsys DesignWare HBM3, PHY e IP de verificação assim como o modelo de emulação de memória ZeBu, sistema de prototipagem HAPS e 3DIC Compiler já estão disponíveis.

«fim do comunicado à imprensa»