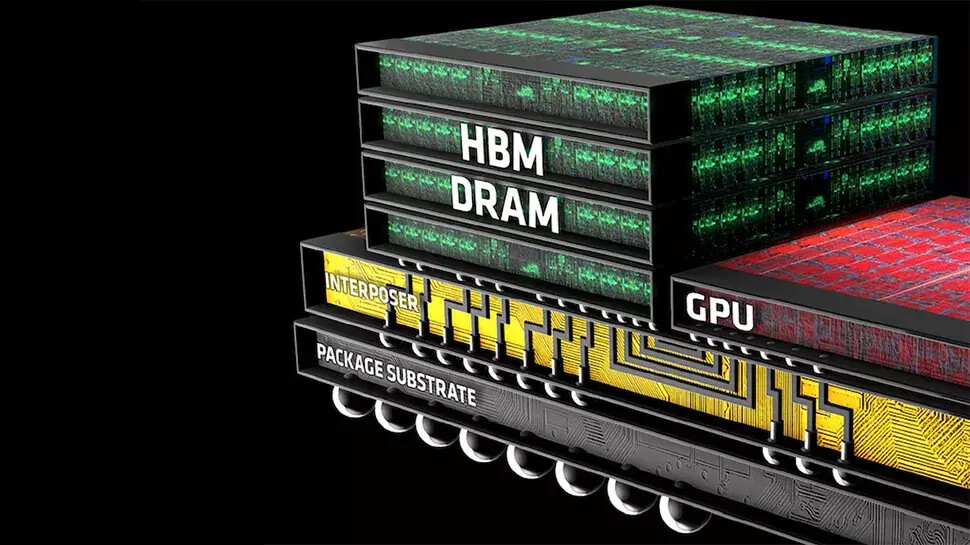

Hoje vemos o anúncio da Synopsys, Inc. sobre sua mais nova tecnologia e soluções para designers de chips. Como pioneira no setor, a empresa lançou suas mais novas soluções HBM3 IP, consistindo em PHY, controlador e IP para verificação de pacotes de múltiplos moldes 2,5D. Essa tecnologia aumentará ainda mais o desenvolvimento de especificações de potência mínima e largura de banda alta para arquiteturas SoC voltadas para IA eficiente e de alto processamento, computação e aplicativos para gráficos.

O controlador DesignWare da Synopsys e empurra IP”alto largura de banda da memória de até 921 GB/s.”Inédito na indústria de chips, o Synopsys Verification IP e a solução utilizam cobertura interna, bem como padrões de verificação, opções de memória HBM3 para emuladores ZeBu (disponíveis no mercado) e um design de protótipo HAPS exclusivo para seus sistemas para verificar informações de HMB3 IP para sistema em chips. A empresa aumenta os desenvolvimentos para seus projetos HBM3, fazendo com que a plataforma do compilador 3DIC para uso de múltiplas matrizes para uma”exploração arquitetônica totalmente integrada, implementação e solução de análise em nível de sistema”.

Synopsys cria nova interface física para DDR5 e memória DDR4

“A Synopsys continua a atender aos requisitos de design e verificação de SoCs com muitos dados com IP de interface de memória de alta qualidade e soluções de verificação para os protocolos mais avançados, como HBM3, DDR5 e LPDDR5. As soluções completas de verificação e IP HBM3 permitem que os designers atendam aos crescentes requisitos de largura de banda, latência e energia enquanto aceleram o fechamento da verificação, tudo de um único provedor confiável.”

—John Koeter, vice-presidente sênior de marketing da Synopsys e Estratégia para IP

Synopsys DesignWare HBM3 PHY IP é um processo de 5 nm e está disponível como PHY pré-fabricado ou configurável pelo cliente, operando a velocidades de 7200 Mbps por pino pn chip, im comprovando eficiência de energia e suporta até”quatro estados operacionais ativos”, permitindo frequências de escalonamento dinâmico. O DesignWare usa um micro bump array que é otimizado para auxiliar na minimização da área. O suporte para os comprimentos de rastreamento do interposer permite aos fabricantes mais espaço em colocações PHY para não impactar seu desempenho.

O amplo portfólio DesignWare IP da Synopsys inclui bibliotecas lógicas, memórias incorporadas, sensores PVT, teste incorporado, IP analógico, IP de interface, IP de segurança, processadores integrados e subsistemas. Para acelerar a prototipagem, o desenvolvimento de software e a integração de IP em SoCs, a iniciativa IP Accelerated da Synopsys oferece kits de prototipagem de IP, kits de desenvolvimento de software de IP e subsistemas de IP. Nosso amplo investimento em qualidade IP e suporte técnico abrangente permitem que os designers reduzam o risco de integração e acelere o tempo de colocação no mercado.