Het zag er slecht genoeg uit voor Huawei in mei 2019 toen de VS het op de entiteitenlijst zetten als nationaal bedreiging van de veiligheid. Als gevolg hiervan had Huawei geen toegang meer tot zijn Amerikaanse toeleveringsketen. Maar precies een jaar later verhinderde een wijziging in de Amerikaanse exportregels dat een gieterij die Amerikaanse technologie gebruikte om chips te bouwen geavanceerde componenten naar Huawei kon verzenden.

Zelfs de chips die Huawei zelf had ontworpen via zijn HiSilicon-eenheid, mochten niet worden verzonden naar de fabrikant die Huawei dwong zijn Kirin 9000 5G-chips te rantsoeneren. En voor sommige modellen moest het zich wenden tot Qualcomm’s Snapdragon 888, maar zonder ondersteuning voor 5G. En nu de chipindustrie volgend jaar overstapt naar het 3nm-procesknooppunt, hoe kunnen Huawei-telefoons dan concurrerend blijven als het verbannen blijft om geavanceerde chips te ontvangen?

Huawei is van plan te kijken naar chipstapeling om concurrerend te blijven

Volgens een Weibo-bericht (via Gizchina), Guo, de huidige roterende voorzitter van Huawei Ping zei onlangs op de jaarlijkse rapportconferentie van 2021 dat het bedrijf chipstapeltechnologieën zal gebruiken, waardoor het SoC’s kan gebruiken die zijn gebouwd met minder geavanceerde processen en toch de prestaties kunnen evenaren van chips die zijn gemaakt met behulp van meer geavanceerde procesknooppunten. Er zijn enkele kanttekeningen waarmee Huawei te maken zal krijgen als het dit plan doorzet.

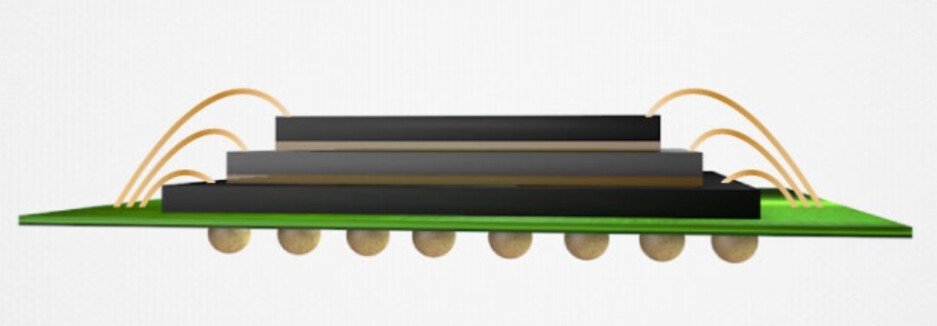

Basisafbeelding van het stapelen van chips met matrijzen van verschillende grootte. Credit MasterBond

Het stapelen van chips neemt meer”ruimte”in een telefoon in beslag en kan ook extra warmte genereren. Bovendien kan deze technologie minder ruimte overlaten om een batterij met grote capaciteit in te persen. Zoals u zich kunt voorstellen, is het stapelen van chips het proces waarbij chips verticaal worden gemonteerd om de prestaties te verbeteren en de beschikbare ruimte beter te gebruiken.

Chipstapelen met matrijzen van dezelfde grootte

Tijdens het beantwoorden van vragen liet de Huawei-topman doorschemeren dat het bedrijf zelfvoorzienend kan zijn wat chips betreft:”In 2019 bedroegen de verzendingen van Huawei’s mobiele telefoons 120 miljoen eenheden, wat betekent dat 120 miljoen mobiele telefoons chips nodig hebben. In 2019 bedroegen de verzendingen van het 5G-basisstation van Huawei 1 miljoen eenheden. Als elk basisstation er een nodig heeft chip, het heeft 1 miljoen nodig. De twee orden van grootte zijn totaal verschillend. Huawei kan concurrerend zijn in toekomstige producten. We zullen in deze richting blijven werken.”

Eerder deze maand, Nikkei Asia meldden dat drie grote bedrijven die gieterijen runnen, TSMC, Samsung en Intel, kondigde de oprichting aan van een consortium dat zich zal concentreren op geavanceerde chipverpakking en chipstapeling. Momenteel is het toevoegen van meer transistors aan een chip de manier om krachtigere componenten te produceren. Maar uiteindelijk zal het verkleinen van de transistors een punt bereiken waarop het niet meer kan en dat betekent het einde van de wet van Moore.

Vooruitgang in chipverpakkingen zou de wet van Moore levend kunnen houden

Je hebt misschien wel eens gehoord van de wet van Moore. Het is een observatie van Intel en de medeoprichter van Fairchild Semiconductor, Gordon Moore. In 1965 realiseerde Moore zich dat het aantal transistors op een dicht geïntegreerd circuit elk jaar verdubbelt. In 1975 herzag Moore de wet van Moore, waarin werd opgeroepen om het aantal transistoren om de twee jaar te verdubbelen. En nu we de beperkingen van de transistorgrootte bereiken, gebruikt de industrie meer hersenkracht dan de aanwezigen op een Wordle-conventie in een poging te voorkomen dat de wet wordt’ingetrokken’.

Verpakking is een gebied waar we meer zouden kunnen zien innovatie op korte termijn. Het consortium hoopt de Universal Chiplet Interconnect Express (UCIe) op te zetten, een nieuw ecosysteem te creëren en andere samenwerkingen in de verpakkings-en stapelsegmenten te helpen vormen. Op zoek naar een betere muizenval in termen van chipverpakking leiden bedrijven als TSMC, Samsung en IBM de ontwikkeling van Vertical Transport Field Effect Transistors (VTFET) die verticaal op een chip worden gestapeld.

Bij VTFET worden de transistors loodrecht op elkaar geplaatst en de stroom loopt verticaal. IBM en Samsung zeggen dat dit ontwerp ook zal leiden tot minder verspilde energie door een grotere stroomsterkte. Volgens de twee technologiebedrijven zullen chips die gebruikmaken van de VTFET-transistors twee keer zo snel presteren als eerdere componenten of 85% minder energie verbruiken dan chips die worden aangedreven door FinFET-transistors.

Google en AMD maken ook deel uit van het consortium met Samsung, Intel en TSMC. Hoewel Apple geen lid is, vertrouwt laatstgenoemde op TSMC om veel van zijn chipontwerpen te bouwen, waaronder de A-serie en M-serie chips.