.fb-comments,.fb-comments span,.fb-comments span iframe[style]{min-width:100%!important;width:100% !important}

Innhold

Optimalisert 3nm-prosess oppnår 45 % redusert bruksevne, 23 % forbedret funksjonalitet og 16 % mer kompakt overflateområde i motsetning til 5nm-tilnærming

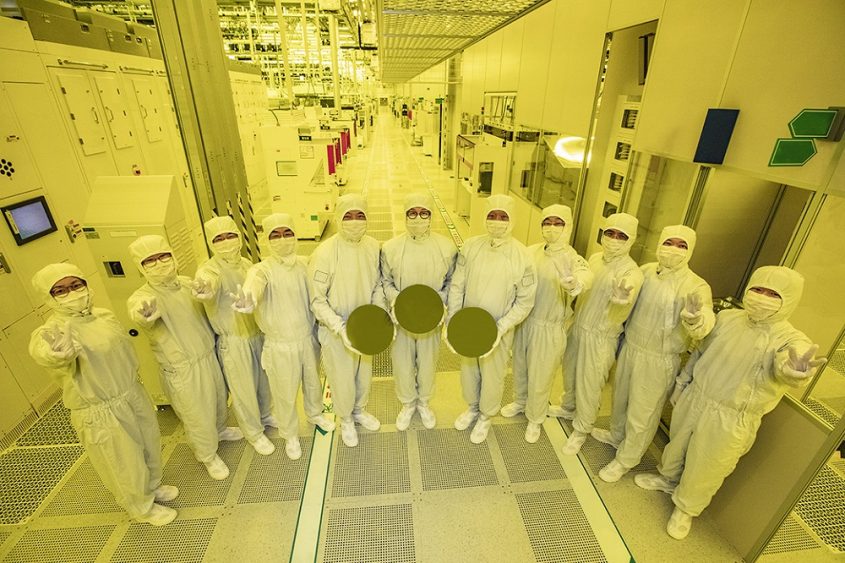

▲ Lederne for Samsung Foundry Company og Semiconductor R&D Heart holder tre fingre oppe som et bilde av 3nm som feirer selskapets første til enhver tid utgang på 3nm handlingsforløp med GAA-arkitektur.

Samsung Electronics, verdenssjefen innen halvlederteknikk, introduserte akkurat nå at det har startet foreløpig produksjon av sin 3-nanometer (nm) handlingsnode som bruker Gate-All-All around (GAA) transist eller arkitektur.

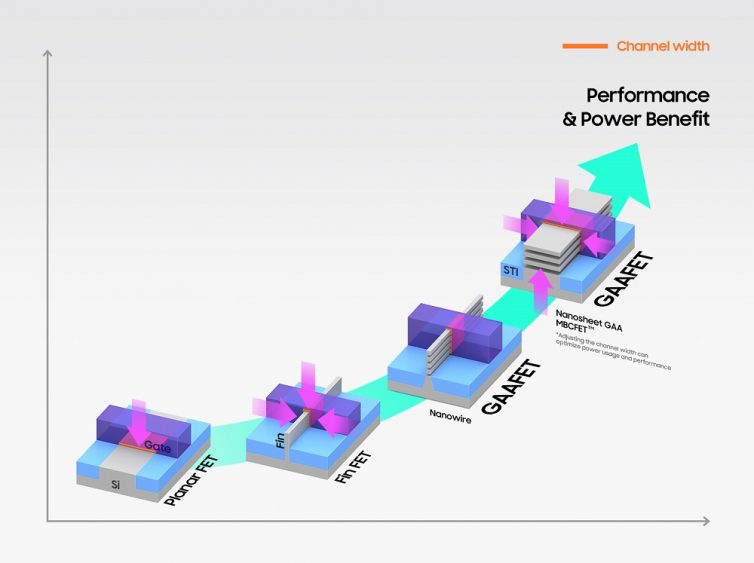

Multi-Bridge-Channel FET (MBCFET™), Samsungs GAA-teknologi som ble brukt på det opprinnelige tidspunktet til enhver tid, trosser de generelle ytelsesbegrensningene til FinFET, og styrker evneytelsen ved å redusere kildespenningsgraden , selv om det også øker effektiviteten ved å øke den nyeste kapasiteten.

Samsung setter opp den aller første applikasjonen av nanosheettransistoren med halvlederbrikker for betydelig generell ytelse, minimal energidatabehandling og ideer for utvikling til mobile prosessorer.

“Samsung har vokst raskt ettersom vi fortsetter å demonstrere lederskap i å bruke kommende epoker-systemer til produksjon, slike som støperiindustriens opprinnelige Substantial-K Metallic Gate, FinFET, like godt som EUV. Vi søker etter å fortsette denne ledelsen med verdens opprinnelige 3nm-prosess med MBCFET™,” hevdet Dr. Siyoung Choi, president og leder av støperibedriften hos Samsung Electronics.”Vi vil fortsette med livlig innovasjon innen aggressiv teknologiforbedring og bygge prosesser som støtter fremskyndet utvikling av modenhet.”

▲ (Fra venstre) Michael Jeong, konserndirektør Ja-Hum Ku, konserndirektør og Sang Bom Kang, konserndirektør President i Samsung Foundry Small business holder opp 3nm wafere ved utgangslinjen til Samsung Electronics Hwaseong Campus.

Design-teknologisk kunnskap Optimalisering for maksimert PPA

Samsungs proprietære teknologier bruker nanoark med bredere kanaler, som tillater større generell ytelse og større energieffektivitet i motsetning til GAA-teknologier som bruker nanotråder med smalere kanaler. Ved å bruke den 3nm GAA teknologiske kunnskapen, vil Samsung være klar til å endre kanalbredden på nanoarket ved kjøp for å forbedre funksjonsbruk og generell ytelse for å møte ulike forbrukerønsker.

I tillegg, stilen og designtilpasningsevnen til GAA er veldig nyttig for Structure Engineering Co-Optimization (DTCO),1 som vil bidra til å forbedre energi, effektivitet, plass (PPA) fordeler. Sammenlignet med 5nm-metoden kan den første teknologiske 3nm-prosessen redusere strømforbruket med opptil 45 %, forbedre effektiviteten med 23 % og redusere regionen med 16 % i motsetning til 5nm, når neste tids 3nm-system skal redusere energibruken med opptil 50 %, foreta forbedringer av den totale ytelsen med 30 % og redusere plass med 35 %.

Leverer 3nm stil-og designinfrastruktur og leverandører med Risk-free™ partnere

Når teknologiske kunnskapsnoder blir mindre og generelle ytelseskrav til brikker utvikler seg høyere, har IC-designere problemer med å håndtere utrolige mengder informasjon for å bekrefte avanserte elementer med flere funksjoner og tettere skalering. For å møte denne typen behov, streber Samsung etter å tilby et mye mer stabilt naturlig miljø for å hjelpe til med å kutte ned tiden som kreves for stil og design, verifisering og sign-off prosess, samtidig som produktet eller tjenestens pålitelighet økes.

Fordi 3. kvartal 2021 har Samsung Electronics levert verifisert stilinfrastruktur ved hjelp av grundige forberedelser med Samsung høyt utviklede Foundry Ecosystem (Secure™)-medarbeidere som inkluderer Ansys, Cadence, Siemens og Synopsys, for å gjøre det mulig for shoppere varen deres i et minimalt tidsintervall.

Priser fra Secure™ Partners

Ansys, [John Lee, visepresident og daglig leder for Electronics, Semiconductor & Optics Business Unit hos Ansys]

“Sammen fortsetter Ansys og Samsung å produsere muliggjør teknologisk innovasjon for de mest innovative mønstrene, nå på 3nm med GAA teknologisk know-ho w. Signoff-troskapen til vårt Ansys multifysikk-simuleringssystem er et bevis på vårt pågående partnerskap med Samsung Foundry i fremste kant. Ansys forblir forpliktet til å levere den ideelle stilkunnskapen for våre felles sofistikerte kunder.»

Cadence, [Tom Beckley, Senior Vice President og General Manager, Custom IC & PCB Group at Cadence]

“Vi gratulerer Samsung med denne milepælen for lansering av 3nm GAA-utgang. Cadence jobbet intenst sammen med Samsung Foundry for å hjelpe kundene med å oppnå best mulig elektrisk kraft, ytelse og plassering for denne noden og arbeidet med våre elektroniske remedier fra bibliotekkarakterisering til fullstendig elektronisk flytimplementering og signoff, alt drevet av våre Cadence Cerebrus AI-baserte teknologier for å optimalisere produktivitet. Med våre tilpassede remedier samarbeidet vi med Samsung for å hjelpe og validere en full AMS-strøm for å øke produktiviteten fra kretsdesign og stil og simulering ved hjelp av automatisk format. Vi ser frem til å fortsette dette samarbeidet for å oppnå langt flere tapeout-suksesser.»

Siemens EDA, [Joe Sawicki, Executive Vice President for IC-EDA-segmentet av Siemens Digital Industries Software]

“Siemens EDA er glad for å ha samarbeidet med Samsung for å hjelpe til med å sikre at våre eksisterende programvareplattformer også fungerer på Samsungs nye 3-nanometer systemnode gitt at det første utviklingsstadiet. Vårt langvarige partnerskap med Samsung etter Secure™-planen genererer store fordeler for våre gjensidige kjøpere, ved sertifisering av Siemens forretnings-hoved EDA-utstyr ved 3nm.»

Synopsys, [Shankar Krishnamoorthy, daglig leder og Corporate Staff for Silicon Realization Group at Synopsys]

“Gjennom vårt langvarige, strategiske samarbeid med Samsung Foundry, gjør vi det mulig for våre svar å hjelpe Samsungs toppmoderne prosedyrer, og oppmuntrer våre gjensidige kjøpere til drastisk hastighet opp sine stilsykluser. Vår assistanse for Samsungs 3nm-metode med GAA-arkitektur utvides, nå med våre Synopsys Digital Design, Analog Style og IP-elementer, som gjør det mulig for klienter å tilby differensierte SoC-er for viktige dataformål med overlegen effektivitet.»

1 For mye mer informasjon og fakta om stil og design Engineering Co-Optimization (DTCO), sørg for å se under tilbakelenker:

Kom over det optimale for det mest effektive. Del 1

Oppdag det eksepsjonelle for det aller beste. Del 2

Vurder dette innlegget

Deling er omsorgsfull!