Na targach CES 2020 firma Intel przedstawiła podgląd nadchodzących telefonów Procesory do komputerów PC o kryptonimie „Tiger Lake”. Oczekuje się, że nowe możliwości Tiger Lake, zbudowane w oparciu o proces 10 nm + firmy Intel i zintegrowane z nową architekturą graficzną Intel Xe, przyniosą ogromne korzyści w porównaniu z procesorami Intel Core 10. generacji. Pierwsze systemy mają pojawić się w tym roku. (Kredyt: Tim Herman/Intel Corporation)

TDP nadchodzących dwunastej generacji procesorów mobilności Alder Lake firmy Intel zostały szczegółowo opisane w najnowszym Poprawka Linux Coreboot . Wykryte przez Coelacanth-dream (via HardwareTimes ), TDP ujawniają wartości TDP Alder Lake-M i Alder Lake-P firmy Intel, które pozornie będą równie wysokie jako istniejące chipy Tiger Lake.

Procesory Intel Alder Lake 10nm Mobility oferują TDP do 115 W, szczegółowe wartości zarówno Alder Lake-P, jak i Alder Lake-M

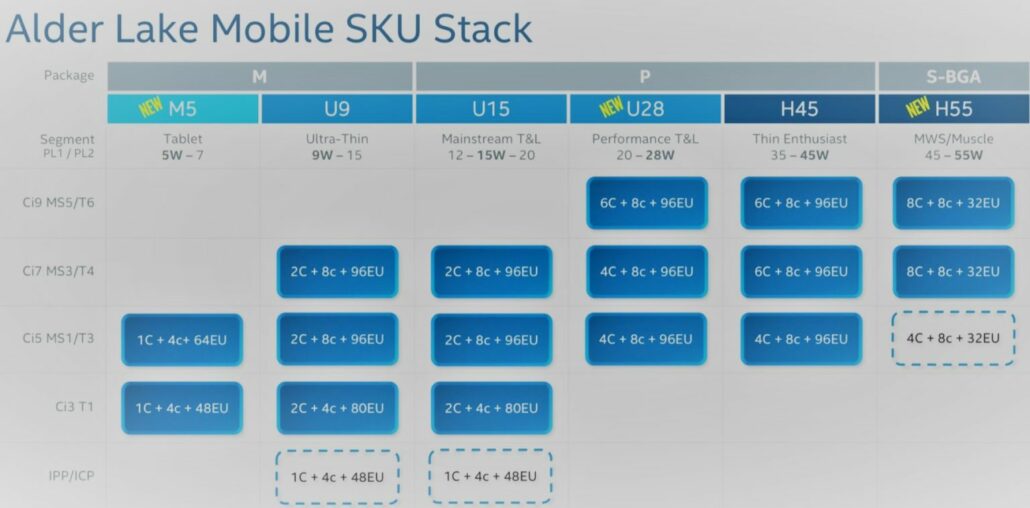

Już szczegółowo opisaliśmy matryce rodziny mobilności Alder Lake jakiś czas temu, a teraz możemy porozmawiać o bardziej istotnych danych dotyczących TDP. Po raz kolejny rodzina mobilności Intela zostanie podzielona na różne segmenty, zaczynając od najlepszych chipów H45, U28, U15 i U9. Pierwsze trzy żetony należą do segmentu Alder Lake-P, podczas gdy układy U9 będą częścią segmentu Alder Lake-M.

Intel Alder Lake-H ma zastąpić chipy Tiger Lake-H. Nowe procesory będą miały architekturę hybrydową z rdzeniami Golden Cove i Gracemont. Jedną z kluczowych zmian byłby zupełnie nowy węzeł procesu 10 nm Enhanced SuperFin (10 +++) w porównaniu z węzłem 10 nm Super Fin 10 nm firmy Tiger Lake (10 ++). Z pewnością możemy spodziewać się kilku kluczowych ulepszeń wydajności, ale ogólne dane TDP będą takie same.

Oczekuje się, że procesory Intel Alder Lake-H45 Mobility będą miały te same podstawowe TDP PL1 o wartości 45 W, ale TDP PL2 zostaną ustawione na 115 W. Chipy Intel Tiger Lake-H mają ocenę PL2 wynoszącą 109 W, a Core i9-11980HK jest jedynym wyjątkiem, który ma ocenę 135 W (profil wydajności). Jest bardzo prawdopodobne, że podobnie jak Tiger Lake-H, Alder Lake-H będzie również zawierał SKU do overclockingu dla laptopów z wyższej półki, który będzie również miał podobny profil wydajności i wyższą ocenę TDP. Mapa drogowa dla stacków ujawniła wyższej klasy SKU z oceną PL1 55W.

Następnie mamy kody SKU Alder Lake-P z serii U. Jednostki SKU U28 będą miały moc znamionową 28 W PL1 i 64 W PL2, podczas gdy jednostki SKU U15 będą miały oceny PL1 i 55 W PL2. Schematy blokowe pokazały konfigurację 4 plus 8 rdzeni dla U15 i 6 plus 8 rdzeni dla części U28. Idąc dalej, mamy SKU U9, które są częścią segmentu ultra-niskiego TDP (Alder Lake-M). Jednostka SKU U9 zostanie skonfigurowana z podstawową wartością TDP PL1 wynoszącą 9 W i oceną PL2 wynoszącą 30 W, podczas gdy jednostki SKU M5 otrzymają TDP PL1 5 W i około ~ 20 W TDP PL2. Poniższa tabela pokazuje, jak wartości TDP wypadają w porównaniu z chipami mobilności Tiger Lake.

TDP procesorów Intel Alder Lake i Tiger Lake Mobility

| Segment procesora | PL1 TDP | PL2 TDP | Rdzenie/wątki |

|---|---|---|---|

| Alder Lake-H55 | 55 W/45 W | > 115 W | 12/16? |

| Alder Lake-H45 | 45 W/35 W | 115 W | 12/16? |

| Tiger Lake-H45 | 45 W | 109 W (i7-11800H) 135 W (i9-11980HK) |

8/16 |

| Alder Lake-U28 | 20 W/28 W | 64 W | 12/16? |

| Tiger Lake-U28 | 28 W | 54 W (i7-1185G7) | 4/8 |

| Alder Lake-U15 | 15 W/20 W | 55 W | 4/12? |

| Tiger Lake-U15 | 15 W | 44 W (Core i7-1180G7) | 4/8 |

| Alder Lake-U9 | 9 W/15 W | 30 W | 5/6? |

| Tiger Lake-U9 | 9 W | 28 W | 4/8 |

| Alder Lake-M5 | 7 W/5 W | ~ 20 W | 5/6? |

Konfiguracja procesora Big.SMALL 12. generacji Intel Alder Lake:

| CPU | Architektura’Cove’dużych rdzeni | Architektura’Atom’małych rdzeni | Poziom GPU |

|---|---|---|---|

| 8 + 8 + 1 | 8 | 8 | GT1 |

| 8 + 6 + 1 | 8 | 6 | GT1 |

| 8 + 4 + 1 | 8 | 4 | GT1 |

| 8 + 2 + 1 | 8 | 2 | GT1 |

| 8 + 0 + 1 | 8 | 0 | GT1 |

| 6 + 8 + 2 | 6 | 8 | GT2 |

| 6 + 8 + 1 | 6 | 8 | GT1 |

| 6 + 6 + 2 | 6 | 6 | GT2 |

| 6 + 6 + 1 | 6 | 6 | GT1 |

| 6 + 4 + 2 | 6 | 4 | GT2 |

| 6 + 4 + 1 | 6 | 4 | GT1 |

| 6 + 2 + 1 | 6 | 2 | GT1 |

| 6 + 0 + 1 | 6 | 0 | GT1 |

| 4 + 8 + 2 | 4 | 8 | GT2 |

| 4 + 0 + 1 | 4 | 0 | GT1 |

| 2 + 8 + 2,5 | 2 | 8 | GT2.5 |

| 2 + 8 + 2 | 2 | 8 | GT2 |

| 2 + 4 + 2 | 2 | 4 | GT2 |

| 2 + 0 + 2 | 2 | 0 | GT2 |

| 2 + 0 + 1 | 2 | 0 | GT1 |

| 1 + 4 + 1,5 | 1 | 4 | GT1.5 |

| 1 + 4 + 1 | 1 | 4 | GT1 |

Linia procesorów Intel Alder Lake ma zadebiutować jeszcze w tym roku i będzie oferować 20% poprawę IPC nad Rocket Lake, co powinno zapewnić mu konkurencyjną pozycję w stosunku do architektury procesorów AMD Zen 4. Tutaj możesz dowiedzieć się więcej o ulepszeniach architektury, IO i platform, które pojawią się na platformach stacjonarnych i mobilnych 12. generacji.