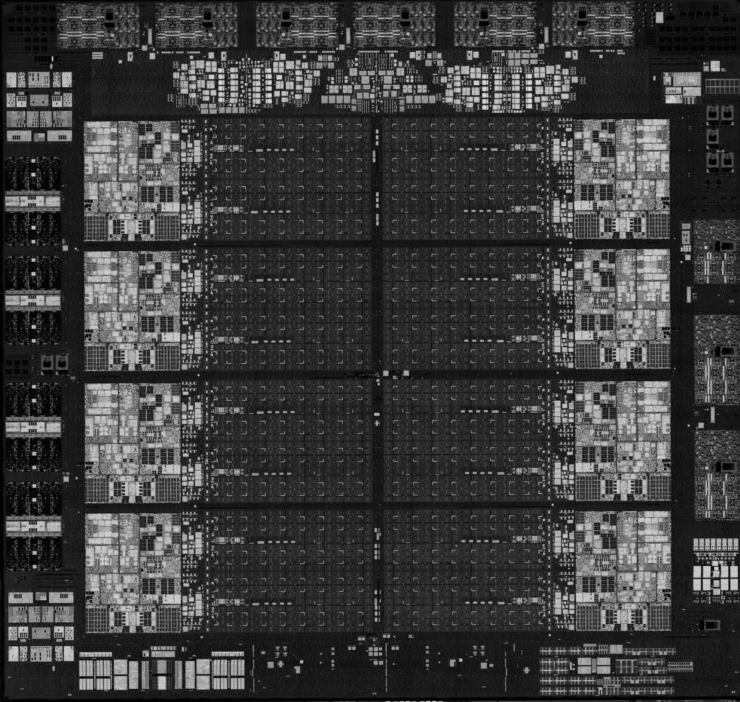

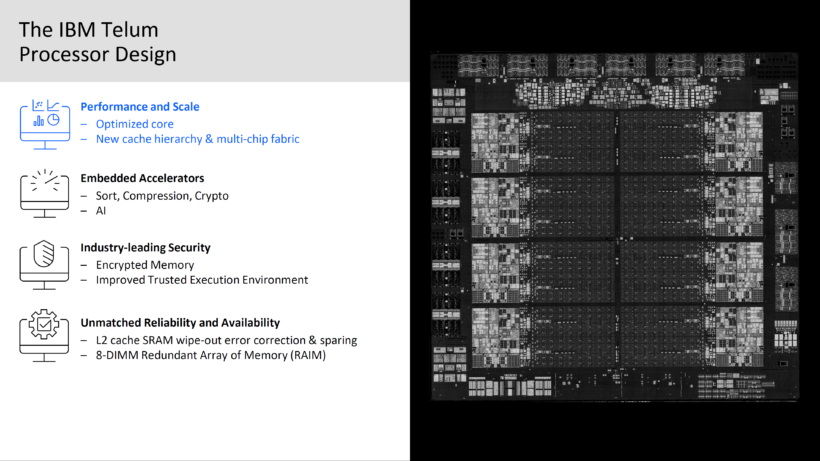

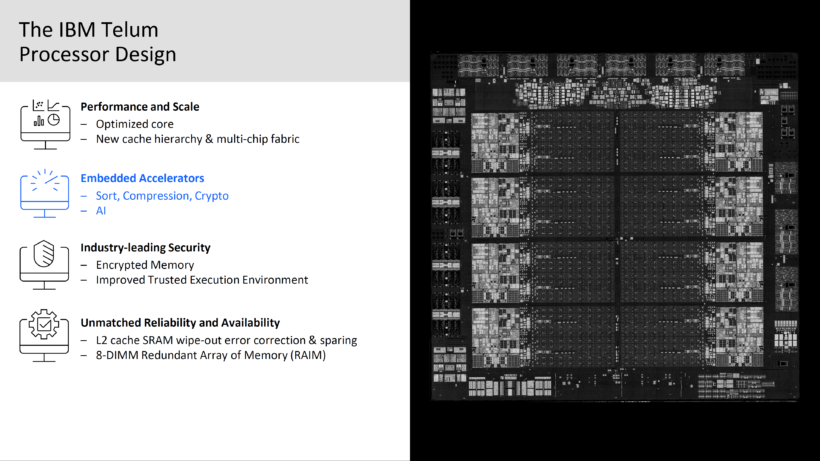

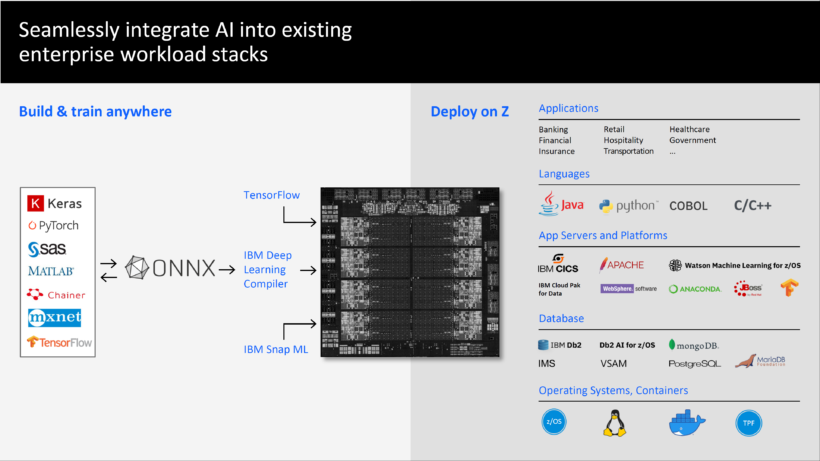

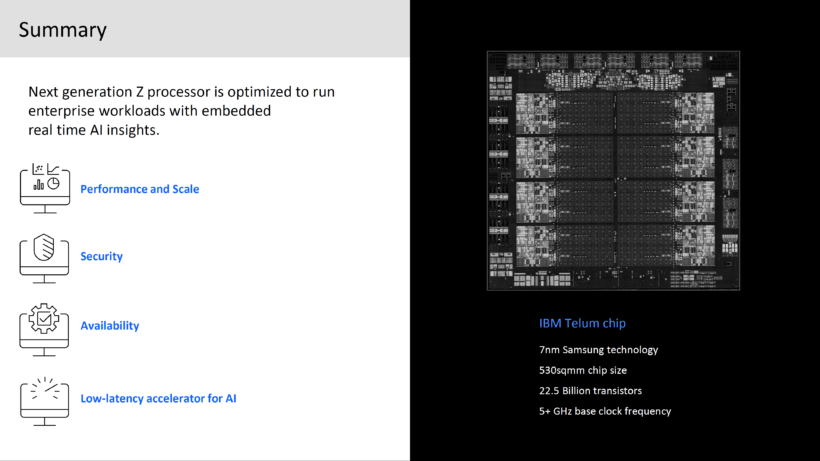

A IBM detalhou seu próximo-geração do chip Telum que faz parte da linha de processadores Z em HotChips 33 . O chip Telum apresenta um novo design de arquitetura de núcleo voltado para aceleração de IA.

Processador Z de próxima geração da IBM: 7 nm Telum Chip com 22,5 bilhões de transistores, 8 núcleos, 5 GHz + relógios e 6+ TFLOPs de aceleração de IA

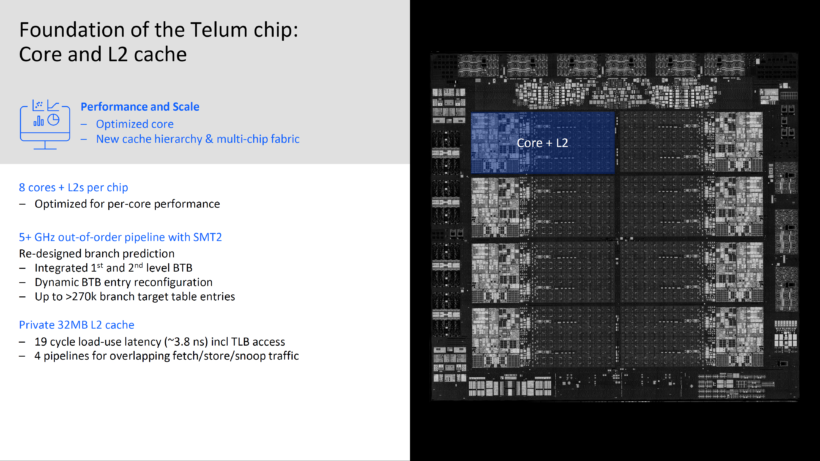

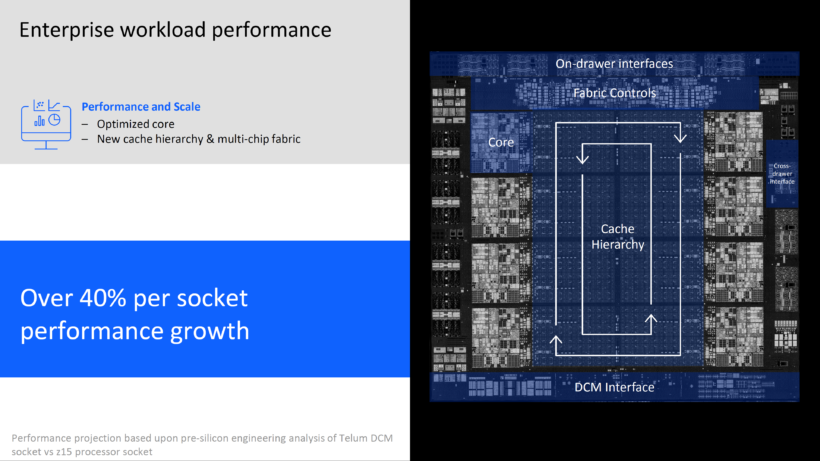

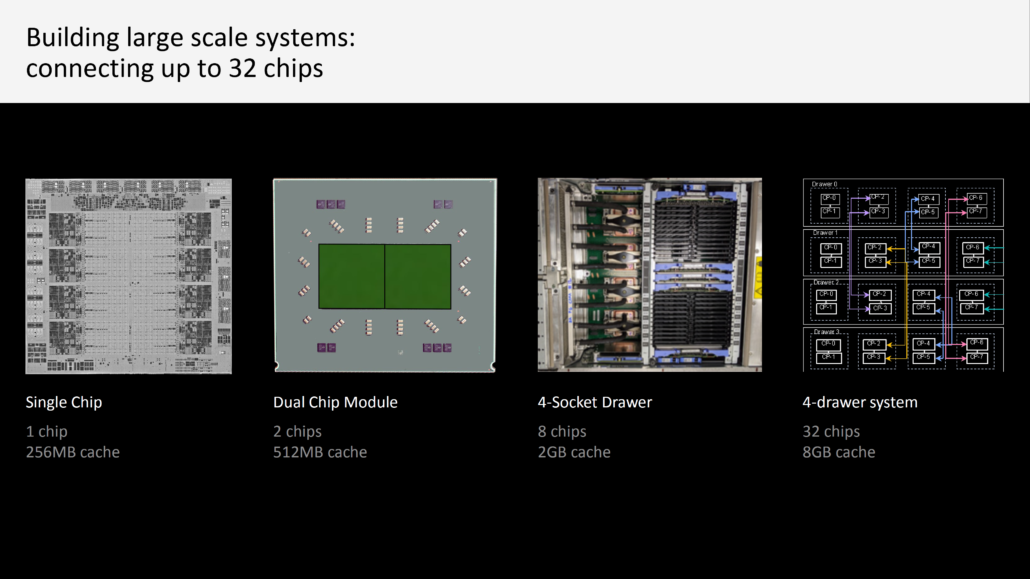

De acordo com a IBM, o núcleo Z recém-otimizado, juntamente com seu novo cache e hierarquia de fabric multi-chip, permite um crescimento de desempenho de mais de 40% por soquete. O chip Telum é composto por um total de 8 núcleos que apresentam seu cache L2 dedicado. O chip possui SMT2, o que dá 16 threads no chip, enquanto uma configuração máxima de 32 núcleos e 64 threads é possível com um sistema de 4 gavetas.

As velocidades de clock são consideradas superiores a 5 GHz, enquanto o chip Telum Z vem com uma previsão de ramificação reprojetada com BTB de 1º/2º nível integrado, reconfiguração de entrada de BTB dinâmica e mais de 270 mil entradas de tabela de destino de ramificação. O cache L2 privado tem um tamanho de 32 MB e apresenta uma latência de uso de carga de 19 ciclos (~ 3,8 ns incluindo acesso TLB).

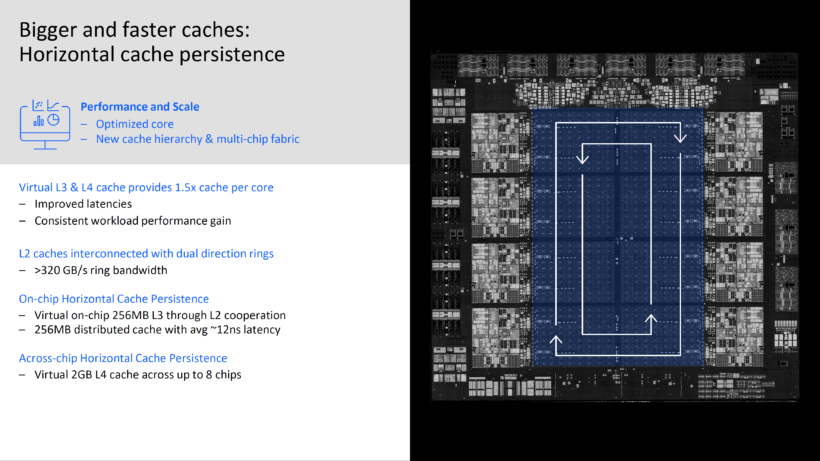

Passando para os caches L3 e L4 que são compartilhados entre os 8 núcleos, o chip IBM Z Telum contém cache virtual L3 de 256 MB no chip e cache L4 virtual de 2 GB em até 8 chips. O cache L2 usa uma topologia de interconexão em anel de dupla direção de 320 GB/s, enquanto o cache L3 é distribuído por meio da cooperação L2 e tem uma latência média de 12ns. O cache virtual L3 e L4 fornece 1,5x cache por núcleo.

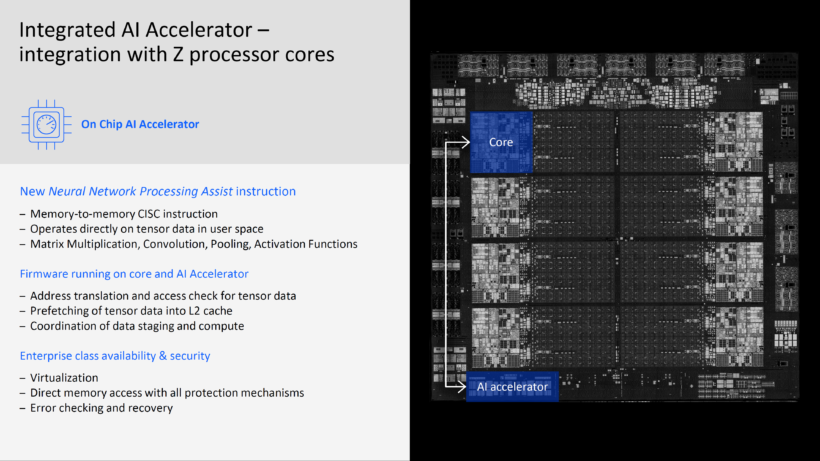

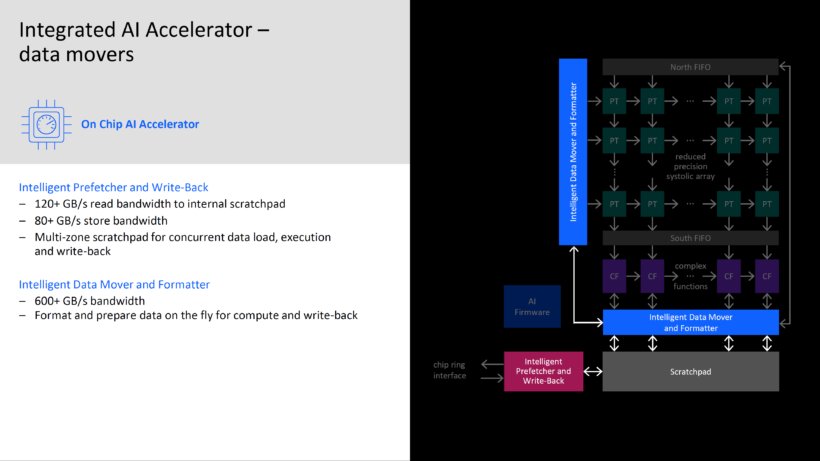

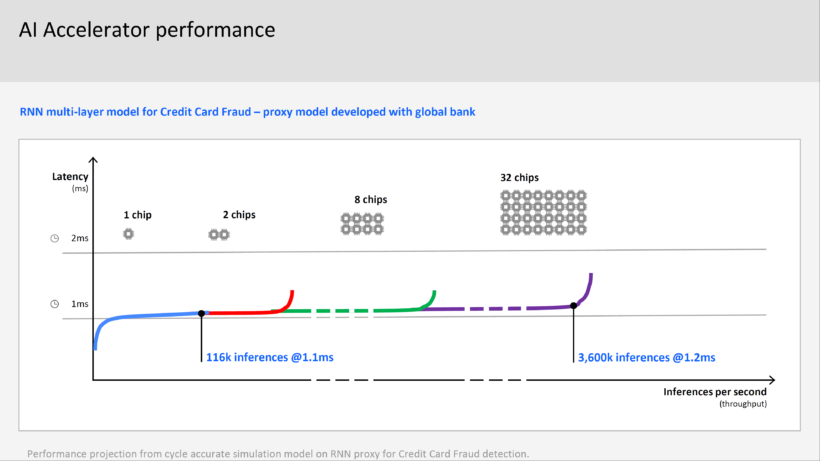

O desempenho no AI Acceleration é avaliado em mais de 6 TFLOPs por chip e mais de 200 TFLOPs em um sistema de 4 gavetas com 4 chips IBM Z. O array Matrix interno possui 128 tiles com 8 vias FP-16 SIMD, multiplicação de alta densidade e acumula FPUs enquanto o Activation Array é composto por 32 tiles com 8 vias FP16/FP-32 SIMD. Uma configuração de chip duplo rende 116.000 inferências (1,1 ms), enquanto uma configuração de 32 chips produz 3.600.000 inferências (1,2 ms).

Os chips IBM Z Telum podem ser escalados para um desempenho ainda maior, pois há ambos únicos projetos modulares de chip duplo e chip. A configuração de 2 chips apresenta um design de chip com 2 chips Telum e oferece 16 núcleos, 32 threads e 512 MB de cache.

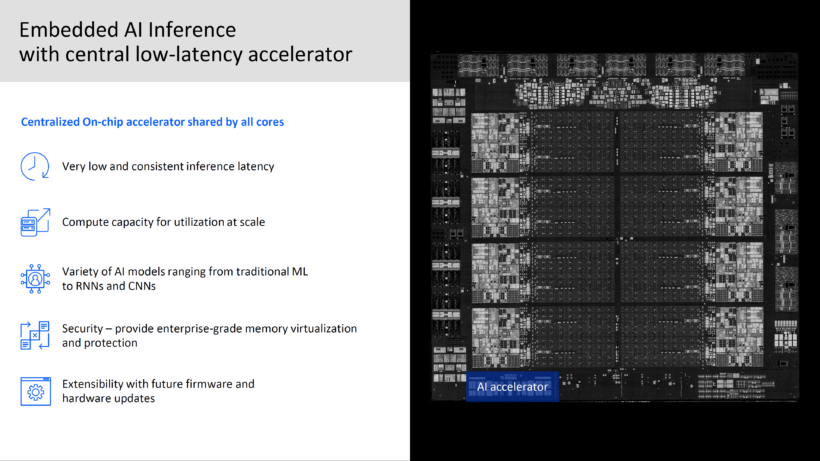

O acelerador de AI no chip IBM Z Telum fornece:

Latência de inferência muito baixa e consistente Capacidade de computação para utilização em escala Variedade de modelos de AI que variam de ML tradicional a RNNs e CNNs Segurança-fornece virtualização e proteção de memória de nível empresarial Extensibilidade com futuras atualizações de firmware e hardware

O chip IBM Z Telum será fabricado no nó de processo Samsung de 7 nm e terá um tamanho de molde de 530 mm2. O chip abrigará 22,5 bilhões de transistores e será voltado para cargas de trabalho incorporadas e corporativas.