Arquitetura AMD RDNA3’para exceder 3 GHz’

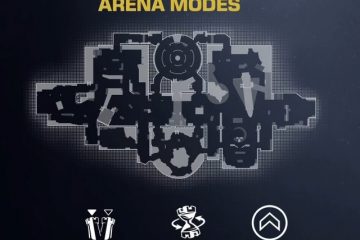

Recebemos uma imagem mostrando o novo diagrama de blocos da GPU Navi 31.

A GPU AMD Navi 31 é um design de chiplet com um GCD (Graphics Compute Die) e seis Memory Cache Dies (MCDs). As matrizes externas abrigam controladores de memória duplos de 32 bits cada, combinados com um grande cache L3. Esses controladores de memória e cache menos críticos foram colocados em um nó TSMC de 6 nm mais barato, enquanto a matriz gráfica principal está usando um nó TSMC de 5 nm.

A AMD confirmou até agora que a GPU Navi 31 completa possui 96 MB de cache L3 (também conhecido como Infinity Cache), mas a empresa ainda não confirmou os caches L0, L1 e L2. Esses são mencionados no novo slide:

L0 – 3 MB – aumento de 240% L1 – 3 MB – aumento de 300% L2 – 6 MB – aumento de 50% L3 (Cache Infinito) – 96 MB (32 MB menor que o Navi 21)

O diagrama mostra o layout do AMD Navi 31 com seis Shader Engine, cada um com 8 unidades de computação duplas. A AMD dobrou a taxa de transferência de computação adicionando SIMD de emissão dupla ao seu design, mas a contagem de núcleos não foi dobrada. É por isso que a contagem do Stream Processor é 6144, mas o desempenho efetivo de computação de precisão simples aumentou para 61 TFLOPS.

O slide também menciona que a arquitetura RDNA3 deve exceder 3 GHz. Isso pode confirmar os relatórios de que a arquitetura foi projetada para escalar até 3,0 GHz, embora o design de referência real não ultrapasse o aumento de 2,5 GHz.

A série AMD Radeon RX 7900 está programada para ser lançada em 13 de dezembro. Não temos certeza se há um embargo separado nos detalhes da arquitetura RDNA3, mas é evidente que há mais slides que ainda podem ver a luz mais cedo.

Muito obrigado ao Sr. Blonde pela foto!

Muito obrigado ao Sr. Blonde pela foto!

Muito obrigado ao Sr. Blonde pela foto!

Muito obrigado ao Sr. Blonde pela foto!

p>