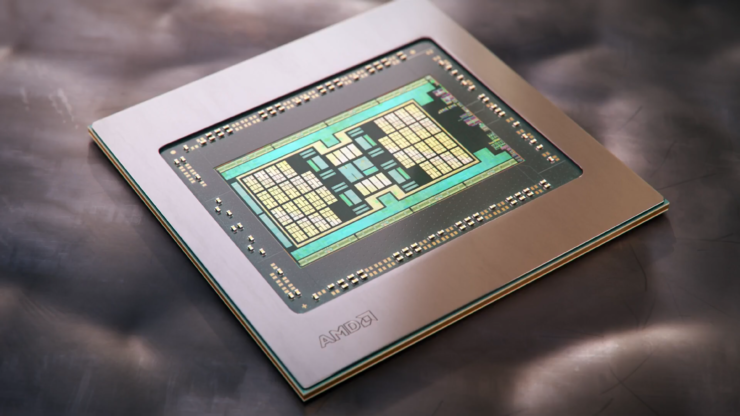

AMD a a publié un nouveau brevet dans lequel la société parle d’un chiplet actif servant de pont entre plusieurs processeurs GPU, probablement basé sur son architecture RDNA 3 de nouvelle génération pour les GPU et les APU.

Le brevet AMD Active Bridge Chiplet pourrait nous donner un aperçu des GPU et APU de nouvelle génération basés sur l’architecture graphique RDNA 3

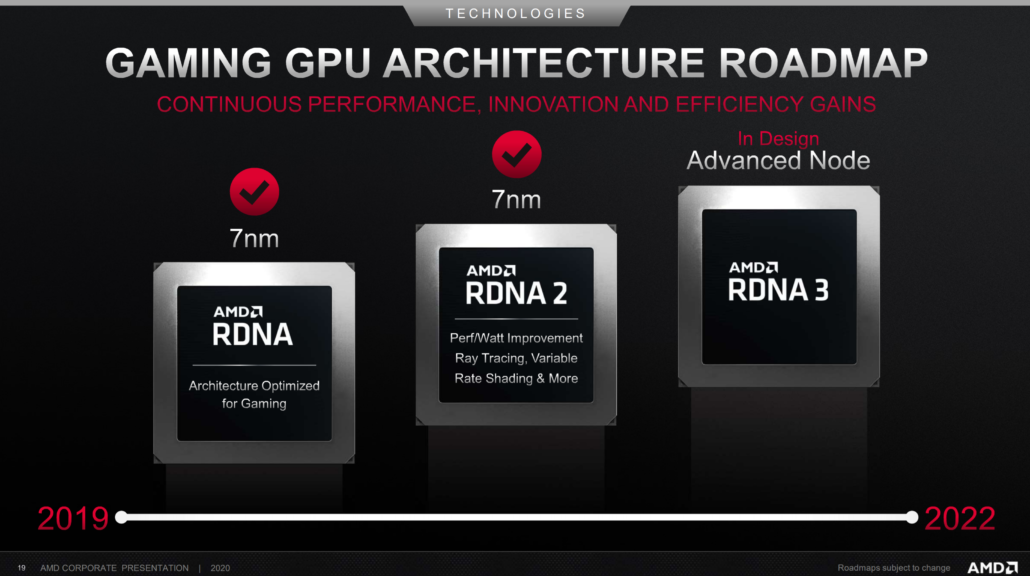

Le brevet commence par indiquer l’éléphant dans la pièce et il s’agit de conceptions GPU monolithiques conventionnelles. Nous savons tous à quel point les chiplets ont fonctionné pour AMD dans le segment des processeurs et la société prévoit maintenant de suivre le même chemin sur le côté GPU . Il n’est pas surprenant que le rival d’AMD, NVIDIA, investisse également dans les conceptions MCM qui sera utilisé dans ses GPU de nouvelle génération. Cela a également du sens car, à l’heure actuelle, l’avancement de la technologie des processus est un facteur crucial et vous ne pouvez pas réduire la taille des GPU autant qu’auparavant, compte tenu de la quantité d’adresses IP différentes qu’un GPU unique emballe ces jours-ci.

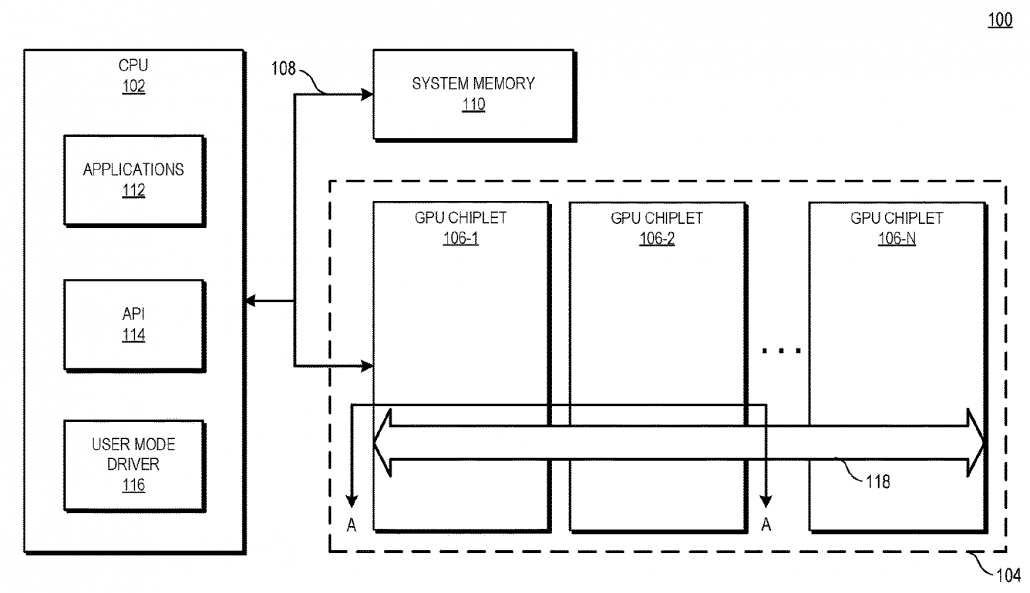

Le schéma de principe illustre un système de traitement 100 utilisant un chiplet de pont actif pour coupler des chiplets GPU conformément à certains modes de réalisation.

La solution d’AMD consiste à investir dans la conception de chipsets pour ses architectures GPU de nouvelle génération. Nous pouvons dire que c’est notre premier regard sur l’architecture RDNA 3 ou une future variante de RDNA. AMD déclare qu’il est confronté à un problème pour faire fonctionner plusieurs GPU en parallèle, pensez à Crossfire qui est une technologie redondante comme le sont toutes les implémentations multi-GPU. Pour résoudre ce problème et faire fonctionner le modèle de programmation pour le chiplet, AMD a proposé un chiplet de pont actif qui relierait plusieurs chiplets de GPU ensemble.

Le schéma de principe principal de la conception conceptuelle montre une puce comportant plusieurs puces. La partie CPU est connectée au premier chiplet GPU via un bus de communication (future génération d’Infinity Fabric) tandis que les chiplets GPU sont interconnectés via le chiplet de pont actif. Il s’agit d’une interface de bus sur puce qui connecte un nombre n de puces GPU. Ce qui est plus intéressant, c’est que le pont comportera également une L3 LLC (Last Level Cache) qui est cohérente et unifiée sur les multiples puces, réduisant ainsi les goulots d’étranglement du cache. Le Chiplet AMD Active Bridge permet donc le fonctionnement parallèle des chiplets sur les modèles de programmation existants et réduit le besoin d’avoir des caches L3 séparés pour chaque Chiplet GPU.

FIG. 2 est un schéma de principe illustrant une vue en coupe des puces GPU et des liaisons croisées passives conformément à certains modes de réalisation.

FIG. 3 est un schéma de principe illustrant une hiérarchie de cache de puces GPU couplées par une réticulation passive conformément à certains modes de réalisation.

FIG. 4 est un schéma de principe illustrant une vue en plan d’étage d’un chipset GPU selon certains modes de réalisation.

FIG. 5 est un schéma de principe illustrant un système de traitement utilisant une configuration à quatre puces conformément à certains modes de réalisation.

Actuellement, le diagramme parle d’une conception de SOC qui laisse entendre qu’il pourrait s’agir d’une conception pour les futurs APU basés sur AMD RDNA 3 pour la mobilité, les plates-formes de bureau et les consoles, cependant, nous devrions également nous attendre à une implémentation similaire sur des GPU discrets pour les ordinateurs de bureau.-mettre à niveau les cartes graphiques et les futurs produits HPC basés sur Architectures CDNA 2 et CDNA 3 . Il sera intéressant de voir cette technologie fonctionner sur les futurs GPU AMD Radeon et Instinct.

Actuellement, AMD propose les solutions Infinity Fabric et Infinity Cache sur sa gamme existante de puces graphiques RDNA 2, de sorte que l’on peut s’attendre à un schéma de dénomination comme Infinity Bridge pour cette solution une fois qu’elle est lancée.