TSMCは、高度なパッケージングテクノロジーのロードマップと次世代のチップレットアーキテクチャとメモリソリューションに対応した次世代のCoWoSソリューションを紹介しました。

TSMCが高度なCoWoSパッケージングテクノロジーロードマップを発表、2023年に設計準備完了チップレットおよびHBM3アーキテクチャの場合

台湾を拠点とする半導体大手は、業界での高度なチップパッケージング技術の展開において急速な進歩を遂げています。 10年以内に、同社は5つの異なる世代のCoWoS(Chip-on-Wafer-on-Substrate)パッケージを発売しました。これらのパッケージは、現在展開されているか、消費者およびサーバースペースに展開されています。

AMDがTSMCになる2番目に大きな顧客–中国で噂されているAppleカーチップの生産

同社は、トランジスタ数を第3世代のパッケージソリューションの20倍に押し上げるGen 5CoWoSパッケージソリューションを今年後半にリリースする予定です。新しいパッケージには、インターポーザー領域が3倍に増加し、最大128 GBの容量に対応する8つのHBM2eスタック、まったく新しいTSVソリューション、Thick CU相互接続、および新しいTIM(Lidパッケージ)が付属します。 TSMCのGen5パッケージングテクノロジーを利用する最も注目すべきソリューションは、AMDのMI200「Aldebaran」GPUです。

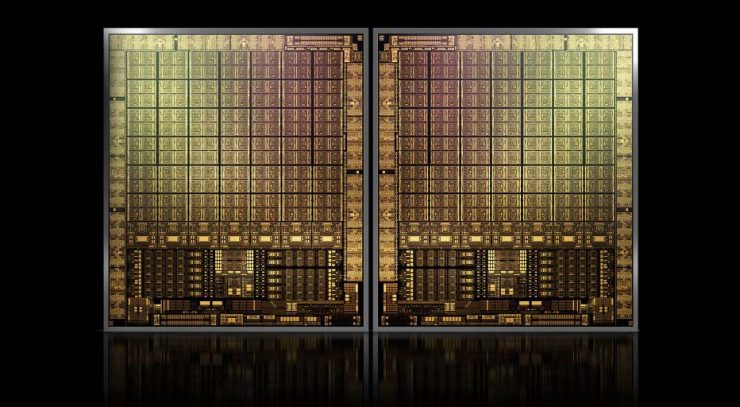

AMD Aldebaran GPUは、TSMCで製造および製造された最初のMCMGPUになります。 GPUはAMDのCDNA2アーキテクチャを搭載し、16,000コア以上や128GBのHBM2Eメモリなどの非常識な仕様を揺るがすことが期待されています。 NVIDIAのホッパーGPUもMCMチップレットアーキテクチャを利用しており、TSMCで生産される予定です。このGPUは2022年に発売される予定であるため、NVIDIAはGen5ソリューションからも活用できると期待できます。

Gen 6までに、TSMCはより多くのチップレットとより多くのDRAMパッケージを統合するためのレチクル領域が大きくなります。パッケージの設計はまだ完成しておらず、TSMCは最大8つのHBM3DRAMと2つのコンピューティングチップレットダイを同じパッケージに収容することを期待しています。 TSMCはまた、メタルティムの形で最新のSOC熱ソリューションを提供する予定です。これにより、パッケージの熱抵抗が第1世代で使用されるゲルTIMの0.15分の1に減少することが期待されます。 N3プロセスノードで製造されるため、CDNA 3(MI300)またはAmpere NextNextのいずれかを検討しています。