昨日の3D V キャッシュ スタック チップレット デザイン、AMD には この技術が来年初めに登場する Zen 3 搭載の Ryzen CPU に導入されることを確認しました。

AMD、Zen 3 3D V-Cache Stack チップレット テクノロジーを搭載した Ryzen CPU が今年後半に生産されることを確認

AMD はこのテクノロジをうまく説明してくれましたが、どの Zen CPU がそれを最初に搭載するかはわかりませんでした。彼らのデモンストレーションには、Zen 3 ベースの Ryzen 9 5900X プロトタイプが含まれており、同社は、3D V-キャッシュ チップ スタッキング テクノロジーが実際に Zen 3 CPU に最初に搭載されることを確認しました。

3D V-Cache Stack チップレット設計の AMD Zen 3 Ryzen CPU

AMDは、テクノロジーがZen 3搭載のCPU、より具体的にはRyzen CPUに向けられることを確認する詳細を提供しました。 CPU は今年後半に生産されるため、2022 年初めのハード ローンチが期待できます。AMD がギアを切り替えて Zen 4 チップに焦点を当てるまでに、少なくとも 2 四半期は残されます。

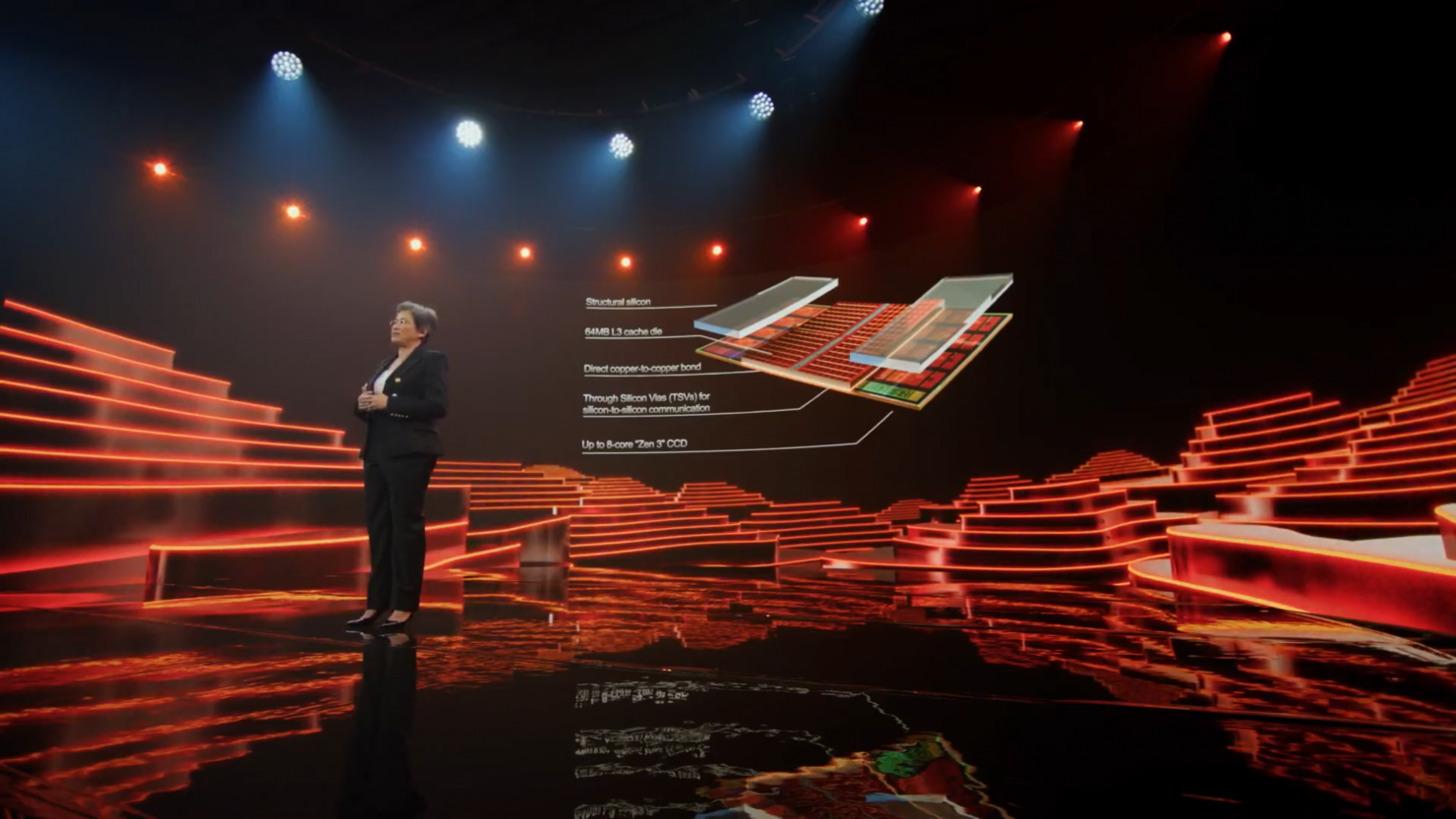

で発表した新しい技術を皆さんが楽しんでくれたことを願っています。 #computex 2021. @AMD Ryzen デスクトップ APU、@Radeon モバイル GPU、FidelityFX スーパー レゾリューション、および当社のまったく新しい 3D チップレット テクノロジー-高性能コンピューティングに最高のものをもたらします!! pic.twitter.com/0memR0kPLu

— リサ・スー (@LisaSu) 2021 年 6 月 1 日

これらがデスクトップまたはモビリティ プロセッサになるかどうかは明言されていませんが、見た目からすると、デスクトップの Ryzen CPU が発生する可能性が高くなります。 AMDは、よりモノリシックなアプローチでコードネームRembrandtの次世代Ryzen APUに焦点を当て、新しいZen 3+コアを搭載すると噂されていますが、RyzenデスクトップCPUは既存のZen 3コアを3D Vキャッシュが追加されて再利用します.

3D V-Cache スタック チップレット デザイン (スタック サイズ/高さ) を備えた AMD Zen 3 Ryzen CPU

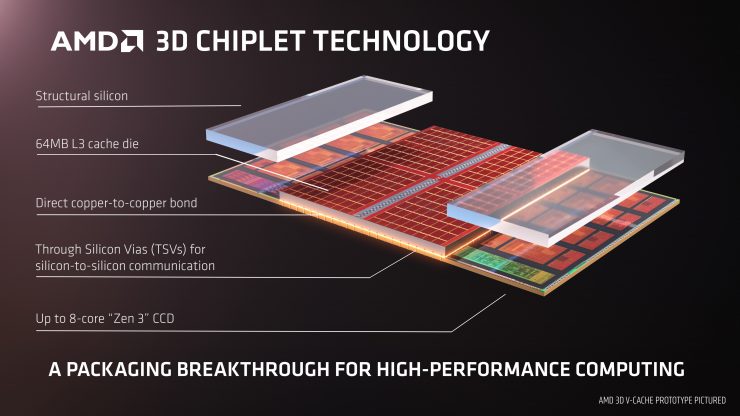

その他の詳細により、単一の 3D V-Cache スタックには、既存の Zen 3 CCD ですでに機能している TSV の上にある 64 MB の L3 キャッシュが組み込まれていることが確認されています。キャッシュは、既存の 32 MB の L3 キャッシュに追加され、CCD ごとに合計 96 MB になります。最初の外出には、チップレットごとに 1 つの 3D V-Cache スタックが含まれるため、最上位の Ryzen SKU で合計 192 MB のキャッシュを見ています。ただし、AMD によると、V-Cache スタックは最大 8-hi まで使用できるため、技術的には、単一の CCD で、Zen 3 CCD ごとに 32 MB のキャッシュに加えて、最大 512 MB の L3 キャッシュを提供できます。

Zen 3 CCD の最初のチップ ショットから TSV サイトがはっきりと見えることを確認しようとしています。

これらは @FritzchensFritz からのショットです。表記を追加しただけです。 pic.twitter.com/rlm17BOQk5

— Andreas Schilling (@aschilling) 2021年6月1日

AMD は Zen 3 CCD と V-Cache を間引いて、コアと IOD の間で高さを変えるのではなく、現在の Zen 3 プロセッサと同じ Z 高さを持つようにしました。 V-Cach は CCD L3 キャッシュの上にあるため、コアの熱出力には影響せず、電源投入時のティックは最小限です。

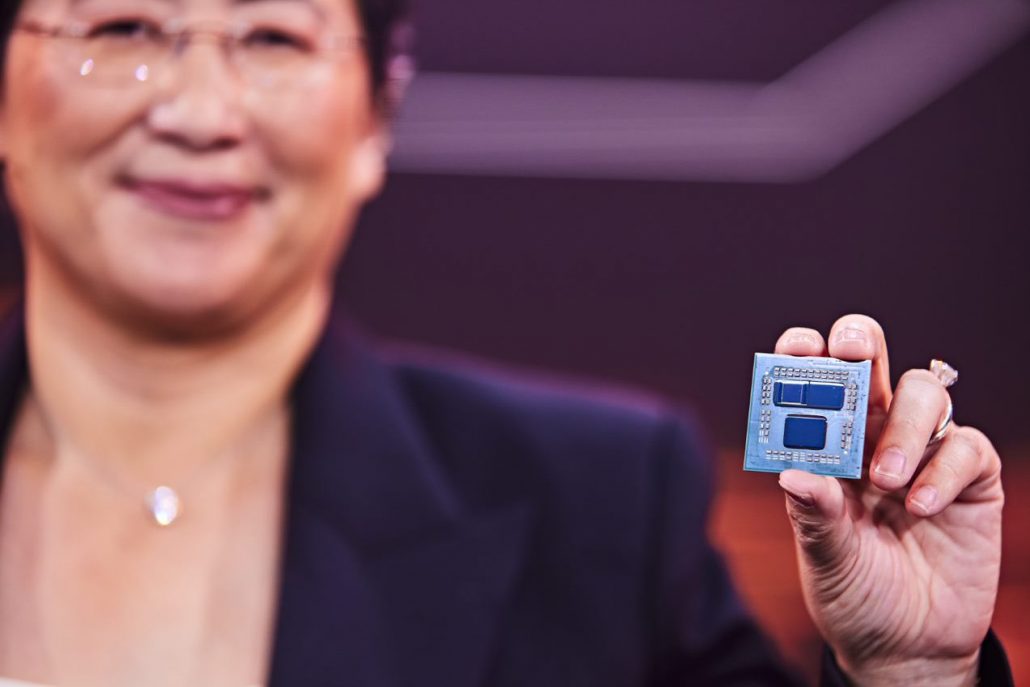

3D V-キャッシュ スタック チップレット デザインを備えた AMD Zen 3 Ryzen CPU (Computex デモ プロトタイプ)

AMD は、チップレット アーキテクチャ ベースの CPU 向けの次世代 3D スタッキング デザインも発表しました。このテクノロジーは、複数のIPを互いに積み重ねることが期待されていますが、AMDによって展示されたプロトタイプには、64MBのL3 SRAMを備えた3D Vキャッシュを備えたRyzen 9 5900Xが含まれていました.

プロトタイプは、6mmx6mm (36mm2) の 3D パッケージ CCD の隣にある標準の Zen 3 CCD を備えています。 CCD のサイズは以前と同じですが、CCD の上に 64 MB のキャッシュを備えた別のパッケージがあり、Zen 3 CCD に既に搭載されている 32 MB の L3 キャッシュに追加されます。

これは、CCDごとに合計96 MBのL3キャッシュ、またはRyzen 9 5950X CPU全体で合計192 MBのL3キャッシュに切り上げられます。 3D V-Cache は、いくつかの TSV を介して CCD に接続されます。 AMD は、このハイブリッド ボンド アプローチにより、200 倍以上の相互接続密度を実現し、全体の効率を 3 倍にすることができると述べています。

3D V-Cache Stack チップレット設計の AMD Zen 3 Ryzen CPU (Computex デモ パフォーマンス)

AMD は、このプロトタイプのデモまで行いました。これは、技術が実際に機能しており、単なる紙のショーケースではないことを意味します。 Ryzen 9 5900X プロトタイプは Gears V を実行していて、ゲームのキャッシュ サイズが増加したおかげで、パフォーマンスが最大 12% 高速になりました。平均して、AMD は 3D V-Cache 設計によりパフォーマンスが 15% 向上すると主張しています。各 V-Cache スタックは、最大 2 TB/秒の全体的な帯域幅を提供します。

AMD は、Intel の Rocket Lake デスクトップ CPU ラインナップと比較して、優れたゲーミング パワーをすでに提供しているため、この追加のパフォーマンス バンプは、Intel が次世代の Alder Lake CPU に賭けてきたすべてを単に打ち砕く可能性があります。

AMD 3D チップレット テクノロジー: ハイ パフォーマンス コンピューティングのパッケージ ブレークスルー。

— AMD (@AMD) 2021年6月1日

AMDは間違いなくZen 4 Ryzen CPUにこの技術を搭載し、今後のZen 3搭載のRyzenとEPYCをパッケージ化するために一歩先を行く Milan-X と最近報告されたスタック 3D V-Cache チップレット噂。