Intelの次世代SapphireRapids Xeon CPUの新しいダイショットが登場し、最大60コアを収容できるMCM設計を示しています。リークは YuuKi-AnS からのものです。第4世代Xeonラインナップを強化するダイ。

Intel Sapphire Rapids Xeon CPUダイショットリークアウト、4つのチップレットと最大56のアクティブな「ゴールデンコーブ」コアを備えたMCM設計

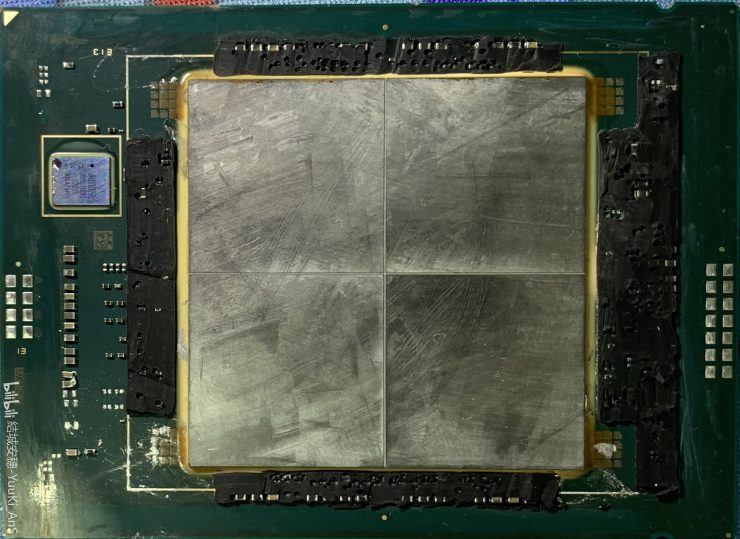

Intelの第4世代SapphireRapids Xeon CPUは先月死にましたが、それらの死の下に何があるのかはわかりませんでした。リーカーは、メイン インターポーザー上の 4 つのチップレット ダイのそれぞれを露出させることに成功しました。 4つのチップレットすべてが露出していると、その下に4×4(1 IMCタイル)コア構成があることがわかります。これは、各ダイが最大15コアで構成されていることを意味します。 16コアである必要がありますが、コア領域の1つがIMCによって占有されているため、合計コアのうち15のみが残り、そのうち1つは歩留まりを向上させるために無効になります。つまり、各ダイは実際には14コアを備え、CPUあたり合計56コアになります。

Intel 第 4 世代 Xeon Sapphire Rapids-SP リーク ダイ ショット (画像クレジット: YuuKi-Ans):

理論的には、IntelのSapphire Rapids-SP Xeon CPUは最大60コアと120スレッドを備えている可能性がありますが、以前のリークから、最大構成は56コアと112スレッドになることがわかっています。前回のリークで、リーカーは、実際のチップでは56コア(ダイあたり14コア)しか有効になっていないのに、合計60コア(ダイあたり15コアまたは5×3レイアウト)を備えたESチップを検討していると述べました。

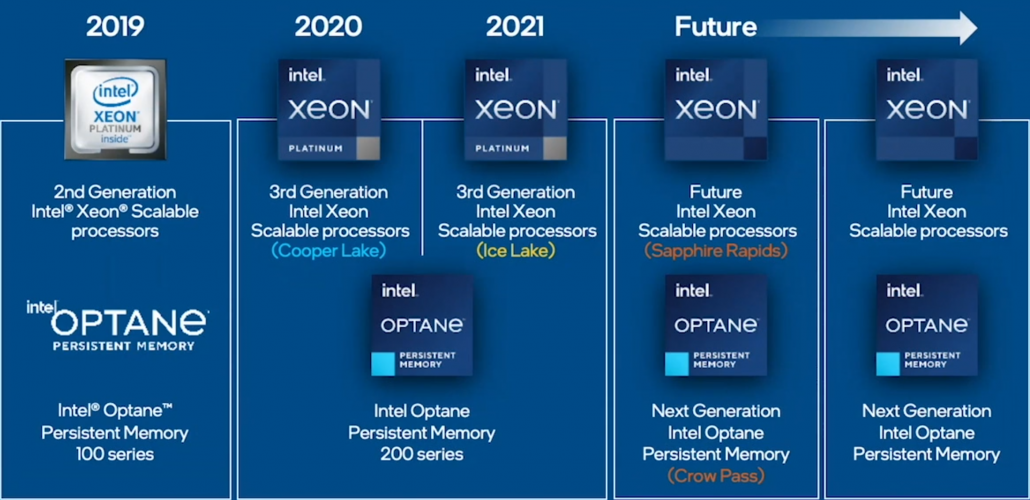

Intel第4世代XeonSapphire Rapids-SPエンジニアリングサンプル(画像クレジット:YuuKi-Ans):

CPUは、最大64 GBの容量(4 x 16 GBスタック)のHBM構成で提供され、DDR5およびPCIe 5.0 I/Oも搭載されます。もう 1 つの興味深い点は、LGA4677 チップが金メッキ IHS を特徴とし、液体金属 TIM を使用したはんだ付け設計を特徴としていることです。 Sapphire Rapids チップ上の IHS もまったく新しいものですが、チップ自体は以前の Xeon 製品で見られたのと同じ長方形になっています。

Intelの第4世代SapphireRapids XeonCPUについて知っていることはすべてここにあります

Sapphire Rapids-SP ファミリーは Ice Lake-SP ファミリーに取って代わり、今年後半に Alder Lake コンシューマー ファミリーで正式にデビューする 10nm Enhanced SuperFin プロセス ノードにすべて搭載されます。これまでのところ、IntelのSapphire Rapids-SPラインナップは、Golden Coveアーキテクチャを利用することが期待されており、10nm EnhancedSuperFinプロセスノードに基づいています。

SapphireRapidsのラインナップは、最大4800 MHzの速度の8チャネルDDR5メモリを利用し、EagleStreamプラットフォームでPCIeGen5.0をサポートします。 Eagle Streamプラットフォームは、LGA 4677ソケットも導入します。これは、それぞれCooperLake-SPおよびIceLake-SPプロセッサを収容するIntelの次期CedarIsland&WhitleyプラットフォームのLGA4189ソケットに置き換わるものです。 Intel Sapphire Rapids-SP Xeon CPUには、サーバーセグメントのブルーチームにとって大きなマイルストーンとなるCXL1.1相互接続も付属します。

構成に入ると、上部は350WのTDPを備えた56コアを備え始めています。この構成で興味深いのは、低ビン分割バリアントとしてリストされていることです。これは、タイルまたはMCMデザインを使用することを意味します。 Sapphire Rapids-SP Xeon CPUは、4タイルのレイアウトで構成され、各タイルにはそれぞれ14コアが搭載されています。

AMDはCPUごとに提供されるコアとスレッドの数で依然として優位に立っており、Genoaチップは最大96コアをプッシュしますが、IntelXeonチップは計画しない場合は56コアで最大になりますタイルの数が多いSKUを作成します。 Intelは、一度に最大8個のCPUをサポートできる、より広く拡張可能なプラットフォームを備えているため、Genoaが2P(デュアルソケット)構成を超えない限り、Intelは8Sラックパッキングでラックあたりのコア数が最も多いでしょう。最大 448 コアと 896 スレッド。

Intel Saphhire Rapids CPU には、最大メモリが 64 GB (それぞれ 16 GB) の 4 つの HBM2 スタックが含まれます。これらのスタックからの合計帯域幅は1TB/sになります。 AdoredTV 、HBM2、GDDR5は、フラット、キャッシング/2LM、ハイブリッドモードで連携できます。ダイのすぐ近くにメモリが存在することは、巨大なデータセットを必要とし、基本的にL4キャッシュとして機能する特定のワークロードに対して絶対的な驚異をもたらします。

Intelは、2022年にSapphire Rapids Xeonスケーラブルファミリの発売に注力していますが、ボリュームランプは2022年初頭まで期待されていません。

Intel Xeon SP ファミリ:

| ファミリーブランディング | Cooper Lake-SP | Ice Lake-SP | |||||

|---|---|---|---|---|---|---|---|

| 14nm+ | 14nm++ | 14nm++ | 10nm + | 10nm Enhanced SuperFin? | 10nm Enhanced SuperFin? | 7nm? | sub-7nm? |

| Intel Purley | Intel Cedar Island | Intel Whitley | |||||

| MCP (マルチチップ パッケージ) SKU | いいえ | ||||||

| LGA 3647 | LGA 4189 | LGA 4189 | LGA 4677 | LGA 4677 | LGA 4677 | 未定 | |

| 28名まで | 28名まで | 40名まで | TBD | ||||

| TBD | |||||||

| 38.5 MB L3 | 38.5 MB L3 | 60 MB L3 | TBD | TBD | TBD | TBD | |

| 最大 8 チャネル DDR4-3200 | 最大 8 チャネル DDR5-4800 | 最大8チャンネルDDR5-5200? | |||||

| PCIe 3.0(48レーン) | PCIe 6.0? | PCIe 6.0? | |||||

| TDP範囲 | 165W-205W | 150W-250W | 105-270W | 350Wまで? | TBD | TBD | |

| Apache パス | バーロー パス | バーロー パス | クロウパス | クロウパス? | ドナヒューパス? | ドナヒューパス? | |

| AMD EPYC Rome 7nm | AMD EPYC Rome 7nm | AMD EPYCミラノ7nm + | AMD EPYCジェノア〜5nm | AMD次世代EPYC(ポストジェノア) | AMD次世代EPYC(ポストジェノバ) | AMD次世代EPYC(ポストジェノバ) | |

| 2018 | 2020 | 2021 | 2021-2022? | 2022? | 2023? | 2024? |

<!-#tablepress-840キャッシュから->