AMD は、Ryzen 9 5900X CPU での V-Cache パッキング テクノロジーを紹介します

AMD は、Computex で最新のイノベーションを発表しました。

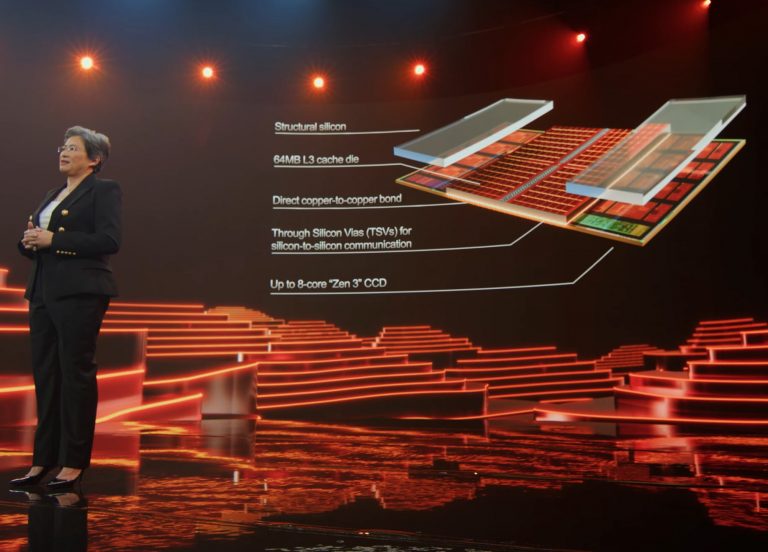

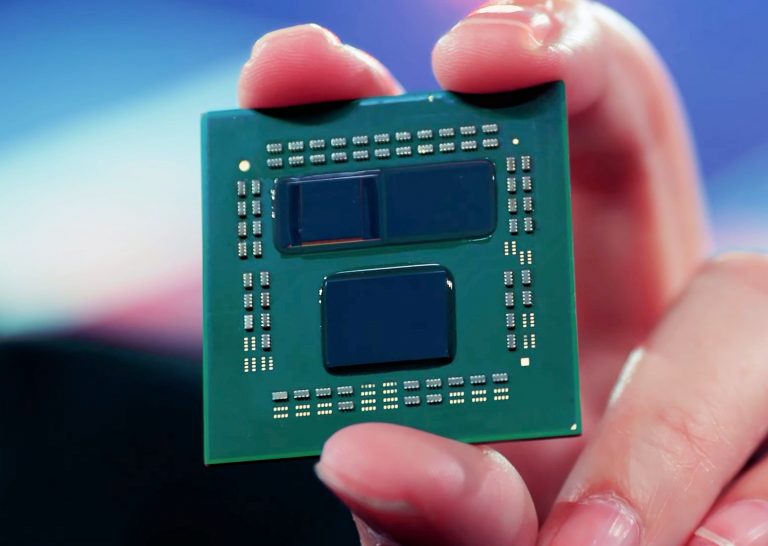

デモ中に、AMD CEO の Dr. Lisa Su は、DRAM スタックを搭載した Zen3 コア アーキテクチャを備えた AMD Ryzen 9 5900X プロセッサのプロトタイプを明らかにしました。コンピューティング タイルの。このスタックは、追加の 64MB の Level3 キャッシュ (SRAM) を提供する 3D V-Cache です。

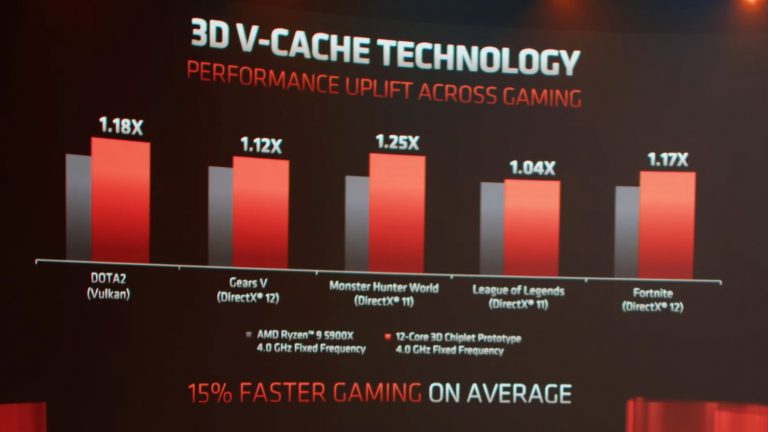

3Dスタッキング技術により、サーバーIPを相互に配置できます。 Computex で示されている例では、プロトタイプの Ryzen CPU に第 3 レベルのキャッシュとして機能する DRAM があります。各 CCD の既存の L3 キャッシュと組み合わせて、5950X などのデュアル CCD Ryzen CPU は、合計 192MB の L3 キャッシュを備えています。このハイブリッド ボンド V-キャッシュ テクノロジーは、相互接続密度を 200 倍向上させ、全体的な効率を 3 倍に向上させます。 AMD によると、4.0 GHz の固定周波数で動作する 12 コアの Ryzen 5900X は、V-Cache を備えた 12 コアの 5900X プロトタイプと比較して、選択したタイトルで平均 15% 高速です。

AMD は、最初の製品がing V-Cache は、今年後半の生産に向けて順調に進んでいます。このスタッキング テクノロジーを搭載した最初の製品が Zen3 または Zen4 アーキテクチャに基づくかどうかは不明です。

チップレットとパッケージングの革新を加速

AMDは、200倍以上の相互接続密度を提供する業界をリードするハイブリッド・ボンド・アプローチを使用して、AMDの革新的なチップレット・アーキテクチャーと3Dスタッキングを組み合わせたパッケージングのブレークスルーであるAMD 3Dチップレット・テクノロジーを使用して、リーダーシップのIPと最先端の製造およびパッケージング・テクノロジーへの投資を引き続き構築2D チップレットの数と、既存の 3D パッケージ ソリューションと比較して 15 倍以上の密度。 TSMCとの緊密な協力により開拓された業界をリードするテクノロジーは、現在の3Dソリューションよりも消費電力が少なく、世界で最も柔軟なアクティブオンアクティブシリコンスタッキングテクノロジーです。AMDはCOMPUTEX 2021 の 3D チップレット テクノロジー – AMD Ryzen™ 5000 シリーズ プロセッサ プロトタイプに結合された 3D 垂直キャッシュで、幅広いアプリケーションで大幅なパフォーマンス向上を実現するように設計されています。 AMDは、今年の終わりまでに3Dチップレットを備えた将来のハイエンド・コンピューティング製品の生産を開始する予定です.

AMD 3D チップレット テクノロジー:-パフォーマンス コンピューティング。

— AMD (@AMD) 2021 年 6 月 1 日