AMDの新しい Ryzenプロセッサ用の3DV-Cacheチップスタッキングテクノロジーは、Computex2021のPC愛好家にとって最も驚くべき発表でした。本日、同社はYouTubeプログラム The Bring Up を介していくつかの詳細を共有しました。これは以下に埋め込まれています。

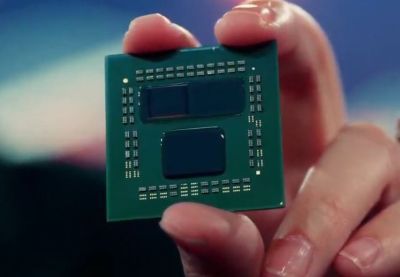

高レベルの3DV-Cacheの概要は、AMDが今年生産を開始するZen3アーキテクチャ用の3Dスタックチップレットを持っているということです。これらの革新的な新しいチップレットは、コア複合ダイ (CCD) の上に垂直にスタックされた 64MB の 7nm SRAM キャッシュ (3D V-キャッシュ) を備えており、CPU コア。

Computex、AMD CEO の Lisa Su は、この技術の概要を共有しました。単一の Ryzen チップで最大 192MB の L3 キャッシュを可能にし、ゲームを最大 15% 向上させます。 Su はまた、同社がすでに稼働している Ryzen 9 5900X チップのプロトタイプを示し、新しいアーキテクチャにより加速されたゲームプレイのかなり印象的なデモを提供しました。

AMDにフォローアップし、同社は3DV-Cacheを搭載したZen3Ryzenプロセッサが今年後半に生産を開始することを確認しました。このテクノロジーは現在、スタックされたL3キャッシュの単一レイヤーで構成されていますが、基盤となるテクノロジーは複数のダイのスタックをサポートしています。また、このテクノロジーは特定のソフトウェアの最適化を必要とせず、レイテンシーとサーマルの観点から透過的である必要があります(どちらにも大きなオーバーヘッドはありません)。

AMDの3Dチップスタッキングテクノロジーは

すでにご存知のように、TSMCのSoICはバンプレスチップスタッキング技術です。つまり、2つのダイを接続するためにマイクロバンプやはんだを使用しません。代わりに、2つのダイは完全に平坦な表面にフライス加工されているため、TSVチャネルはいかなる種類のボンディング材料も使用せずに嵌合でき、キャッシュとコア間の距離が1000分の1に短縮されます。これにより、帯域幅を拡大しながら、熱と電力の消費を削減します。

このビデオにはさらに多くの詳細があり、AMDの新しいスタッキング技術に関するいくつかの詳細とともに、非常に興味深く有益なチップ相互接続技術についての説明があります。見てください。