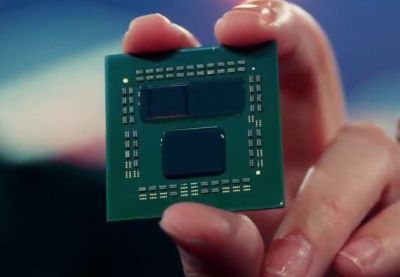

của AMD

Thông báo của AMD về Công nghệ xếp chồng 3D V-Cache dành cho bộ vi xử lý Ryzen dễ dàng là thông báo đáng ngạc nhiên nhất đối với những người đam mê PC tại Computex 2021, và hôm nay công ty đã chia sẻ thêm một số chi tiết thông qua chương trình YouTube The Bring Up mà bạn có thể xem được nhúng bên dưới.

Tổng quan về 3D V-Cache cấp cao là AMD có các chiplet xếp chồng 3D cho kiến trúc Zen 3 sẽ đi vào sản xuất trong năm nay. Những chú chiplet mới sáng tạo này có thêm 64MB bộ nhớ đệm SRAM 7nm (được gọi là 3D V-Cache) được xếp chồng lên nhau theo chiều dọc trên đỉnh phức hợp lõi (CCD) để tăng gấp ba lần bộ nhớ đệm L3 cho Lõi CPU .

Tại Computex, AMD Giám đốc điều hành Lisa Su đã chia sẻ tổng quan về công nghệ này-nó cho phép bộ nhớ đệm L3 lên đến 192MB khổng lồ trên một chip Ryzen duy nhất, giúp cải thiện tới 15% khả năng chơi game. Su cũng cho thấy một chip Ryzen 9 5900X nguyên mẫu mà công ty đã thiết lập và chạy và cung cấp một bản demo khá ấn tượng về lối chơi tăng tốc do kiến trúc mới. Chúng tôi đã liên hệ với AMD và công ty xác nhận rằng bộ vi xử lý Zen 3 Ryzen với 3D V-Cache sẽ được đưa vào sản xuất vào cuối năm nay. Công nghệ hiện chỉ bao gồm một lớp bộ nhớ đệm L3 xếp chồng lên nhau, nhưng công nghệ bên dưới hỗ trợ xếp chồng nhiều khuôn. Công nghệ này cũng không yêu cầu bất kỳ tối ưu hóa phần mềm cụ thể nào và phải minh bạch về độ trễ và nhiệt (cả hai đều không có chi phí đáng kể). Công nghệ xếp chồng chip 3D của AMD dựa trên Công nghệ SoIC của TSMC . Video trên chia sẻ một vài chi tiết thú vị. AMD lật khuôn sau đó cạo khuôn máy tính tiêu chuẩn xuống 95%, chỉ để lại 20 micromet silicon hoạt động cho mục đích tính toán, mỏng hơn sợi tóc người. Sau đó AMD đặt một chip L3 tiêu chuẩn lên trên để hoàn thành ngăn xếp. Như chúng ta đã biết, SoIC của TSMC là một công nghệ xếp chip không gập ghềnh, có nghĩa là nó không sử dụng microbumps hoặc hàn để kết nối hai khuôn. Thay vào đó, hai khuôn được nghiền thành một bề mặt phẳng hoàn hảo đến mức các kênh TSV có thể giao phối mà không cần bất kỳ loại vật liệu liên kết nào, giảm khoảng cách giữa bộ nhớ cache và lõi xuống 1000X. Điều đó làm giảm nhiệt và điện năng tiêu thụ trong khi tăng băng thông. Video có nhiều chi tiết hơn và đi sâu vào phần giải thích về công nghệ kết nối chip, khá thú vị và nhiều thông tin, cùng với một số chi tiết khác về kỹ thuật xếp chồng mới của AMD. Đưa cho nó một chiếc đồng hồ.